|

#1

June 27th, 2016, 11:43 AM

| |||

| |||

| VTU Logic Design Notes

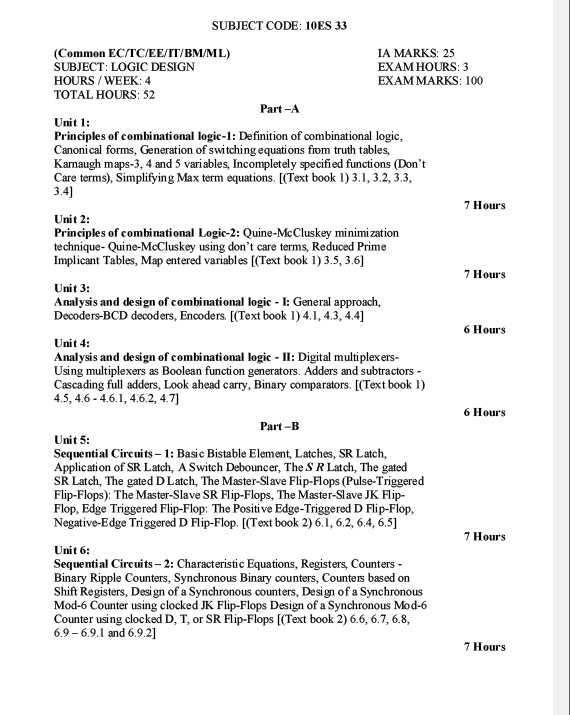

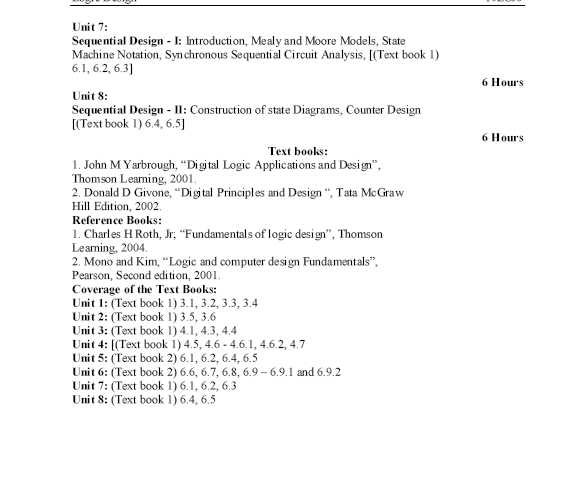

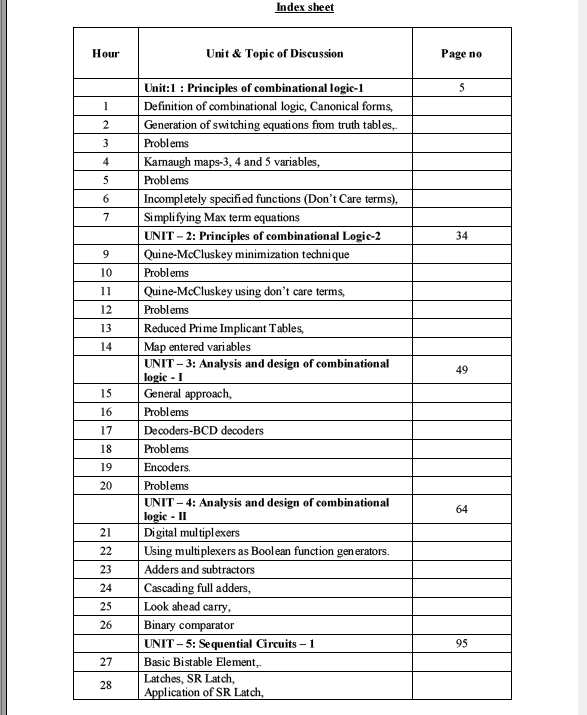

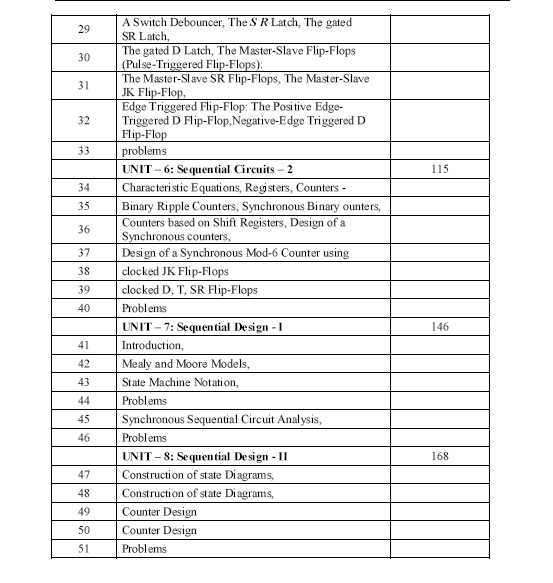

Hello sir I want notes for logic design from VTU. Is there any one can provide me VTU logic design notes for exam preparation? As per my searching I was founded a notes for VTU logic design. Here I’m giving you that notes for preparation: VTU Logic Design Notes      VTU logic design notes: Unit 1: Principles of combinational logic-1: Definition of combinational logic, Canonical forms, Generation of switching equations from truth tables, Karnaugh maps-3, 4 and 5 variables, Incompletely specified functions (Don‟t Care terms), Simplifying Max term equations. Unit 2: Principles of combinational Logic-2: Quine-McCluskey minimization technique- Quine-McCluskey using don‟t care terms, Reduced Prime Implicant Tables, Map entered variables Unit 3: Analysis and design of combinational logic - I: General approach, Decoders-BCD decoders, Encoders. Unit 4: Analysis and design of combinational logic - II: Digital multiplexers Using multiplexers as Boolean function generators. Adders and subtractors - Cascading full adders, Look ahead carry, Binary comparators. Part –B Unit 5: Sequential Circuits – 1: Basic Bistable Element, Latches, SR Latch, Application of SR Latch, A Switch Debouncer, The S R Latch, The gated SR Latch, The gated D Latch, The Master-Slave Flip-Flops (Pulse-Triggered Flip-Flops): The Master-Slave SR Flip-Flops, The Master-Slave JK FlipFlop, Edge Triggered Flip-Flop: The Positive Edge-Triggered D Flip-Flop, Negative-Edge Triggered D Flip-Flop. Unit 6: Sequential Circuits – 2: Characteristic Equations, Registers, Counters - Binary Ripple Counters, Synchronous Binary counters, Counters based on Shift Registers, Design of a Synchronous counters, Design of a Synchronous Mod-6 Counter using clocked JK Flip-Flops Design of a Synchronous Mod-6 Counter using clocked D, T, or SR Flip-Flops Unit 7: Sequential Design - I: Introduction, Mealy and Moore Models, State Machine Notation, Synchronous Sequential Circuit Analysis, Unit 8: Sequential Design - II: Construction of state Diagrams, Counter Design Here I’m giving you VTU logic design notes: Last edited by Neelurk; April 16th, 2020 at 04:14 PM. |