# **Xilinx Tutorial**

Pallavi Paliwal (pallavip@ee.iitb.ac.in) Indian Institute of Technology, Bombay

# Contents

### 1. Introduction to Xilinx

- § Purpose of Xilinx Tool

- § Xilinx Flow Overview

- **§** Available Xilinx Product Families

- **§** Selection Consideration for Xilinx Device

- 2. Creating new ISE Project

### **3.** Synthesizing the Design

- § Understanding Synthesis Process Properties

- § Analyzing Synthesis Report

- § Generating Post-Synthesis Simulation Model

- 4. Specifying User Constraints

- § Understanding Timing Constraints

- § Assigning Package Pins

- 5. Translating the Design

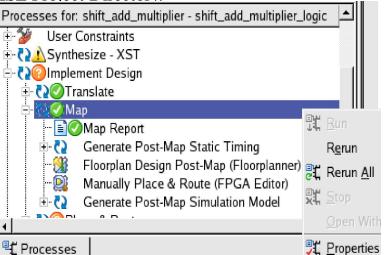

- 6. Mapping the Design

- § Understanding MAP Options

- § Analyzing MAP Report

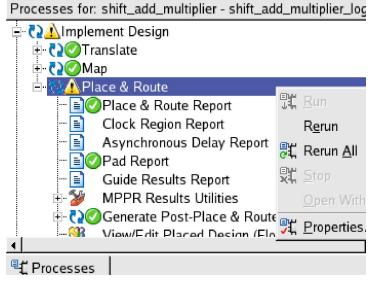

- 7. Placing and Routing the Design

- § Understanding PAR options

- § Analyzing PAR Report

- § Asynchronous Delay Report

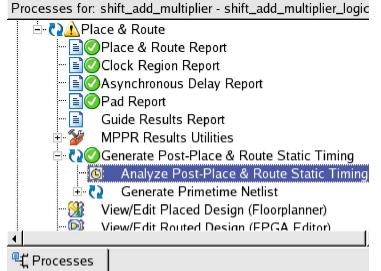

- § Post PAR Static Timing Analysis

- § Generating Post PAR Simulation Model

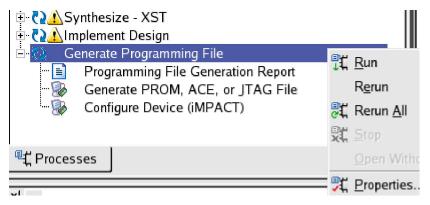

- 8. Generating BitMap File

# Purpose of Xilinx Tool

### **<u>Requirement of Xilinx Tool :</u>**

Xilinx is a Synthesis Tool which converts Schematic/HDL Design Entry into functionally equivalent logic gates on Xilinx FPGA, with optimized speed & area.

So, after specifying behavioral description for HDL, the designer merely has to select the Library and specify Optimization Criteria; and Xilinx Synthesis Tool determines the netlist to meet the specification; which is then converted into Bit-File to be loaded onto FPGA PROM .

Also, Xilinx Tool generates Post-Process Simulation Model after every Implementation Step, which is used to functionally verify generated netlist after processes, like Map, Place & Route.

### Some more Features of Xilinx :

- Allows Mixed Mode HDL Design Entry

- Xilinx ISE allows integration with other Synthesis Engine from Mentor Graphics/Exemplar, Synopsys and Synplicity. (XST is proprietary Synthesis Tool of Xilinx.)

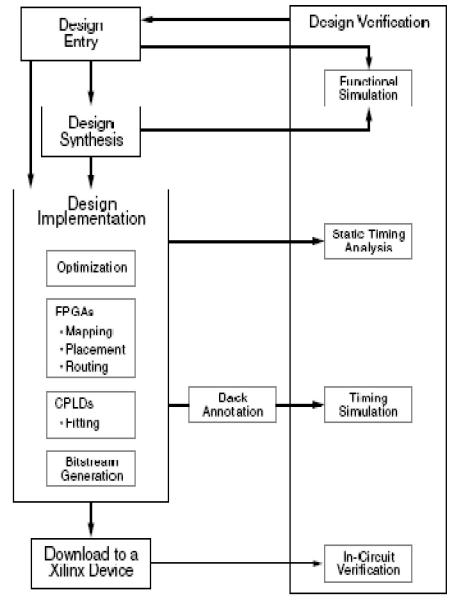

# Xilinx Flow Overview

- Add HDL/Schematic Design Entry to ISE Project, targeted for a particular Xilinx Product Family.

- 2) <u>Design Synthesis</u> : Converts HDL into equivalent boolean equations; according to which logic gates are then correspondingly packed into Logic Cells, LUT's & FF's from Xilinx UNISIM Library

### 3) <u>Design Implementation</u> :

I. Translate : Translate step checks the design and ensures that netlist is consistent with chosen architecture. Translate also checks User-defined Constraint file, for any inconsistencies.

> The above mentioned Process Steps are <u>Technology-Independent Part</u> of Xilinx, since these processes would be carried out successfully by tool, for any product family. (irrespective of the resources available in that particular Xilinx FPGA Product)

[Figure Source: Xilinx ISE 8 Software Manual]

## Xilinx Flow Overview

The following mentioned Implementation Process Steps are <u>Technology Dependent Part</u> of Xilinx, wherein Design could be Mapped, Placed & Routed, with desired Speed & Area constraint, only if Targeted Xilinx Product has required speed grade, sufficient Logic Blocks & Interconnect resources available for Design Entry.

- **II. Map** : Calculates & Allocates Physical Combinational Logic Blocks (CLB) & Input Output Block (IOB) Components in Targeted Device, to Logic Element symbols in Netlist that is generated during Translation Process.

- **III. Place & Route (PAR):** Places CLBs into logical position and utilizes the routing resources on target device, to connect logic cells on Xilinx Product such that desired Timing Specification are met.

- 4) <u>Bit-File Generation</u> : Creates Bit-Stream file containing Configuration Data for Target FPGA Device

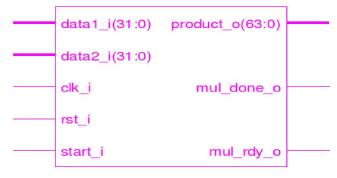

### *Further in this tutorial, Xilinx Flow will be demonstrated through <u>32-bit Shift and Add Multiplier</u> <i>Implementation on Spartan xc3s500e-5-pq208 device.*

This 32-bit Shift & Add Multiplier latches value on Input Data Bus, when START control signal is high; and outputs valid 64-bit Product, while asserting DONE control signal high.

DUT asserts READY control signal, when Multiplier FSM is in idle state.

library IEEE; use IEEE.STD\_LOGIC\_1164.ALL; use IEEE.STD\_LOGIC\_ARITH.ALL; use IEEE.STD\_LOGIC\_UNSIGNED.ALL;

entity shift\_add\_multiplier is

```

port ( data1_i : in std_logic_vector(31 downto 0);-- Multiplicand Input

data2_i : in std_logic_vector(31 downto 0);-- Multiplier Input

product_0 : out std_logic_vector(63 downto 0);-- Data Product output

clk_i : in std_logic;-- Input Clock Signal

rst_i : in std_logic;-- Input Reset Signal

start_i : in std_logic;-- Input START Control Signal

mul_done_0: out std_logic;-- Multiplication DONE Output Control Signal

mul_rdy_0 : out std_logic);-- Multiplier Block READY

```

end shift\_add\_multiplier;

On assertion of Start Input signal, Multiplier Block latches two Input Data

Double Word; and after 32 clock cycles, places multiplied value on 64-bit

product\_o o/p signal, while asserting mul\_done\_o signal (indicating valid

64-bit data product is available on output signal

architecture shift\_add\_multiplier\_logic of shift\_add\_multiplier is

type state\_type is (start\_st,load\_st,shift\_add\_st); -- Multiplier FSM States

signal cur\_state,nxt\_state : state\_type := start\_st; -- FSM Current/Next State Register

signal mul1\_shift\_reg : std\_logic\_vector(63 downto 0); -- Multiplicand Shift Register

signal mul2\_shift\_reg : std\_logic\_vector(31 downto 0); -- Multiplier Shift Register

```

signal product_d1: std_logic_vector(63 downto 0); -- Product 0/P Signal used in

-- Sequential Adder

signal product_d : std_logic_vector(63 downto 0); -- Temporary Product Output from Adder

-- Multiplier O/P is valid only when mul_done_o control signal is asserted

signal mul_done_d : std_logic; -- DONE Control Signal o/p from Combinational Block

-- Input data could be latched by Multiplier block, only when mul_rdy_o signal is high

signal mul_rdy_d : std_logic; -- READY Control Signal o/p from Combinational Block

begin

product_o <= product_d1;</pre>

_____

-- Sequential Logic : Output Data/Control Signals are registered

process(clk_i,rst_i)

begin

-- Reset Multiplier Block asynchronously on Assertion of rst_i signal

if (rst_i = '1') then

cur_state <= start_st ;</pre>

product_d1 <= (others=>'0');

mul_done_o <= '0'

mul_rdv_o <= '0' :

elsif(clk_i'event and clk_i = '1') then

cur_state <= nxt_state ;</pre>

product_d1 <= product_d ;</pre>

mul_done_o <= mul_done_d</pre>

mul_rdy_o <= mul_rdy_d :</pre>

end if:

```

end process;

begin

```

Sequential Logic : Multiplicand & Multiplier Shift Register

process(clk_i,rst_i)

begin

if (rst_i = '1') then -- Asynchronous Reset

mul1_shift_reg <= X"0000_0000_0000" ;</pre>

mul2_shift_reg <= X"0000_0000" ;</pre>

elsif (clk_i'event and clk_i = '1') then

if (nxt_state = load_st) then --Next State as Load acts as Load Enable

--signal for Shift Register

mul1_shift_reg <= X"0000_0000" & data1_i;</pre>

mul2_shift_reg <= data2_i ;</pre>

elsif (nxt_state = shift_add_st) then --Next State as Shift_Add acts as Shift Enable

--signal for Shift Register

mul1_shift_reg <= mul1_shift_reg(62 downto 0) &'0';-- Shift Left Multiplicand</pre>

mul2_shift_reg <= '0' & mul2_shift_reg(31 downto 1); -- Shift Right Multiplier</pre>

end if:

end if:

end process;

_____

FSM Next State Generation Logic

_____

process(cur_state,start_i,mul_done_d)

```

```

case cur_state is

-- On assertion of Start Control I/P , load Input data words

when start_st => if (start_i = '1')then

nxt_state <= load_st ;</pre>

else

nxt_state <= start_st;</pre>

end if:

-- Load State is asserted only for 1 clock cycle

when load_st => nxt_state <= shift_add_st ;</pre>

-- FSM continues to remain in Shift_Add state, depending on width

-- of smaller data byte

when shift_add_st => if (mul_done_d = '1') then

nxt_state <= start_st;</pre>

else

nxt_state <= shift_add_st;</pre>

end if:

when others => nxt_state <= start_st ;</pre>

end case;

end process;

_____

_____

- FSM Output Signal Generation Logic

process(cur_state,mul2_shift_reg,mul1_shift_reg,product_d1)

begin

case cur state is

when start_st => product_d <= (others=>'0');

mul_done_d <= '0'

mul_rdy_d <= '1'</pre>

```

```

when load_st => if (mul2_shift_reg(0) = '1') then-- Multiplier LSB checks whether 0 or shifted

product_d <= mul1_shift_reg ; -- Multiplicand has to be added to temporary</pre>

-- Product Register

else

product_d <= X"0000_0000_0000 ::

end if;

mul_done_d <= '0'</pre>

i

mul_rdv_d <= '0'

when shift_add_st => if (mul2_shift_reg(0) = '1') then

product_d <= product_d1 + mul1_shift_reg;</pre>

else

product_d <= product_d1 ;</pre>

end if:

-- done_d signal asserts when Multiplier Shift Register value is 1

if (mul2_shift_reg = X"0000_0001") then

mul_done_d <= '1';</pre>

mul_rdy_d \ll '1';

else

mul_done_d <= '0';</pre>

mul_rdy_d \ll '0';

end if:

when others => product_d <= X"0000_0000_0000" ;</pre>

mul_done_d <= '0'

mul_rdv_d <= '1'

end case;

end process;

```

```

end shift_add_multiplier_logic;

```

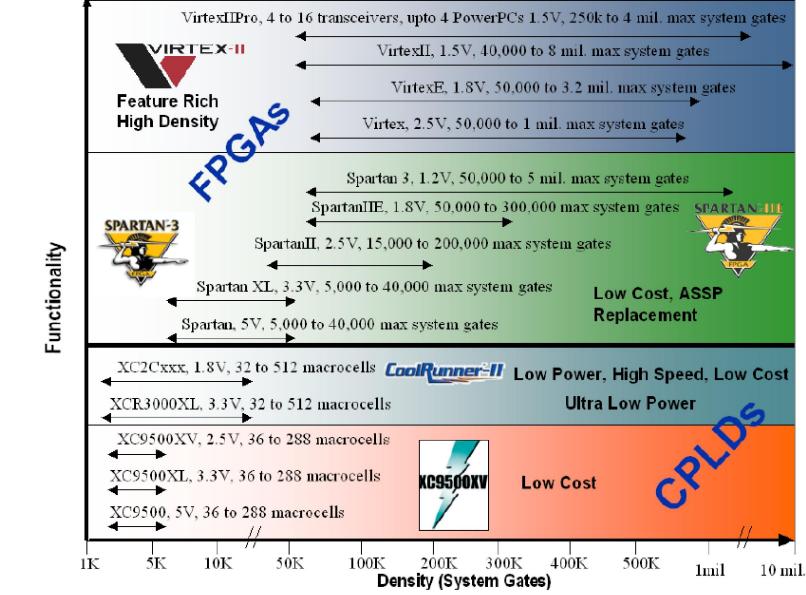

# Available Xilinx Product Families

<sup>[</sup>Figure Source: Programmable Logic Design Quick Start Handbook, By Karen Pawell & Nick Mehta]

- Spartan

- Virtex

- Coolrunner

- XC9500

# Selection Consideration for Xilinx Device

According to Design Specification, decide which device best meets the design criteria. *Selection Consideration in order of general priority are :-*

1. <u>Speed Requirement</u> :- If the Maximum Frequency requirement for the design is not met with a particular Xilinx device, choose a Xilinx device of higher Speed Grade (or) switch to next generation Xilinx Product Family.

For eg. Following is the Speed Comparison of Shift & Add Multiplier synthesized on Spartan Device (with different Speed Grade) & Virtex Device.

| Target Device                      | Maximum Frequency<br>(of Multiplier design) |

|------------------------------------|---------------------------------------------|

| <i>Spartan</i> :- xc3s500e-4-pq208 | 119 MHz                                     |

| <i>Spartan</i> :- xc3s500e-5-pq208 | 137 MHz                                     |

| <i>Virtex</i> :- xc5vlx30-2-ff324  | 259.639 MHz                                 |

| <i>Virtex</i> :-xc5vlx30-3-ff324   | 295.683 MHz                                 |

#### <u>Note</u>:-

i) In Target Device Name, -2/-3/-4/-5 indicates Speed Grade available for the device. (Higher the indicated Speed Grade number, higher is the maximum frequency obtained through that device)

ii) Virtex and Spartan Product Family are indicated by text "vlx" and "s" respectively, in Xilinx Device name.

## Selection Consideration for Xilinx Device

# 2. <u>Logic Density</u> :- Choose the device which has Gate Count and Macro-Cells to meet the Logic Density of the design.

For e.g. Following is Device Utilization Summary of Multiplier Implementation on xc3s500e-5-pq208 device. (Here, number 500 in device name indicates that this device has 500k gates)

Device utilization summary:

| Number of Slices:           | 198 out of 4656 4% |

|-----------------------------|--------------------|

| Number of Slice Flip Flops: | 165 out of 9312 1% |

| Number of 4 input LUTs:     | 379 out of 9312 4% |

| Number of IOs:              | 133                |

| Number of bonded IOBs:      | 133 out of 158 84% |

| Number of GCLKs:            | 1 out of 24 4%     |

(Small Designs like Multiplier can be implemented on CPLD Series having minimum number of gates, amongst available Xilinx Product families)

3. <u>Package Type and Number of IO Pins</u>:- Based on Number of Input/Output Ports of the design, decide on device having sufficient number of IO Pins.

For e.g. 32-bit Multiplier Design cannot be implemented using device 3s500ecp132-5, since, this Chip-Scale Package only has 92 I/O pins, whereas Multiplier design here has 133 I/O ports.

*xc3s500e-5-pq208 device can be used for Multiplier Design because this Plastic Quad Flat Package has 158 I/O Pins.*

# Creating new ISE Project

1. From Project Navigator, select File > New Project.

(Specify the *Project Name*, *Project Location*; and select *Top Level Source Type* as HDL)

2. Click Next & describe <u>Device Properties</u> in New Project Wizard. (Based on the Selection Design Consideration mentioned earlier, select Xilinx Product Family/ Device Type/ Package Type & Speed Grade)

Following image window indicates the Device Properties selected for Shift-Add Multiplier Implementation :-

| 150 | Mew Project Wizard - Device Properties |                                      |  |  |  |  |  |  |  |  |

|-----|----------------------------------------|--------------------------------------|--|--|--|--|--|--|--|--|

| E,  | Select the Device and Design Flow for  | the Project                          |  |  |  |  |  |  |  |  |

|     | Property Name                          | Value                                |  |  |  |  |  |  |  |  |

|     | Product Category                       | All                                  |  |  |  |  |  |  |  |  |

|     | Family                                 | Spartan3E 🗾                          |  |  |  |  |  |  |  |  |

|     | Device                                 | XC3S500E                             |  |  |  |  |  |  |  |  |

|     | Package                                | PQ208                                |  |  |  |  |  |  |  |  |

|     | Speed                                  | -5                                   |  |  |  |  |  |  |  |  |

|     |                                        |                                      |  |  |  |  |  |  |  |  |

|     | Top-Level Source Type                  | HDL                                  |  |  |  |  |  |  |  |  |

|     | Synthesis Tool                         | XST (VHDL/Verilog)                   |  |  |  |  |  |  |  |  |

|     | Simulator                              | Modelsim-SE VHDL                     |  |  |  |  |  |  |  |  |

|     | Preferred Language                     | VHDL 🗾                               |  |  |  |  |  |  |  |  |

|     |                                        |                                      |  |  |  |  |  |  |  |  |

|     | Enable Enhanced Design Summary         | <b>▼</b>                             |  |  |  |  |  |  |  |  |

|     | Enable Message Filtering               |                                      |  |  |  |  |  |  |  |  |

|     | Display Incremental Messages           |                                      |  |  |  |  |  |  |  |  |

|     |                                        |                                      |  |  |  |  |  |  |  |  |

|     | <u>M</u> ore Info                      | < <u>B</u> ack <u>N</u> ext > Cancel |  |  |  |  |  |  |  |  |

3. Click *Next* & then click <u>Add Source</u> tab in New Project Wizard, to browse and add existing HDL source files to current ISE Project

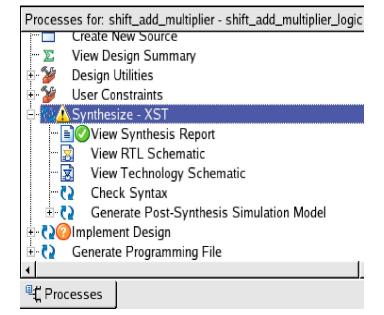

# Synthesizing Design

#### Synthesis Tool Functionality :

During synthesis, HDL files are translated into gates and optimized for the target architecture.

- Thus, XST Synthesis tool uses design's HDL code and generates a supported netlist type (NGC) for Xilinx implementation tools, by performing following general steps :-

- Analyze / Check Syntax of the Source Code.

- Compile : Translates and optimizes the HDL code into a set of components that the synthesis tool can recognize.

- Map : Translates the components from the compile stage into the target technology's primitive components from UNISIM Library.

### Steps to Synthesize HDL Design :

- Select top-level HDL design in the *Sources* window.

- To set Synthesis options, right-click *Synthesize XST* in the *Processes* window; select *Properties* to display the *Process Properties* dialog box.

- With the top-level source file selected, right-click *Synthesize XST* in the Processes window & select *Run* option.

- Synthesis Report file is stored with extension <project\_name>.syr in ISE Project Directory.

## Synthesizing Design – Understanding Synthesis Options

[Source : Xilinx Synthesis and Simulation Design Guide]

Synthesis options enables designer to modify the behaviour of the synthesis tool, to make optimizations according to the needs of design.

- **Optimization Effort :** constraint allows to choose synthesis optimization level as **Normal** or **High** optimization.

- **Optimization Goal :** constraint allows to choose synthesis optimization strategy as **Speed** or **Area**.

For e.g. In Shift Add Multiplier implementation, when **Optimization Goal** is selected as **Area**, though <u>Number of Slices</u> <u>and LUTs</u> utilized reduces by **1%**, but the maximum frequency for the design also reduces by **8MHz**, in comparison to Synthesis done with default Optimization Goal (i.e. Speed).

- <u>Use Synthesis Constraint File</u>: option allows to include (or) exclude .xcf Constraint File ,during synthesis process.

- <u>Keep Hierarchy</u>: is a synthesis and implementation constraint. If hierarchy is maintained during Synthesis, the Implementation tools will use this constraint to preserve the hierarchy throughout the implementation process and allow a simulation netlist to be created with the desired hierarchy. *Though preserving the hierarchy gives the advantage of fast processing; but, merging the hierarchy blocks improves the fitting results (i.e. fewer device macrocells & better frequency*).

- <u>Global Optimization Goal</u>: allows to optimize speed in different regions (register to register, inpad to register, register to outpad, and inpad to outpad) of the design.

- <u>Write Timing Constraints</u>: enables or disables propagation of timing constraints to the NGC file, which will be used during place and route, as well as synthesis optimization.

- <u>Slice Utilization Ratio</u>: defines the area size in absolute number or percent of total number of slices that XST must not exceed, during timing optimization.

## Synthesizing Design – Understanding HDL Options

[Source : Xilinx Synthesis and Simulation Design Guide]

### • <u>RAM / ROM / MUX / DECODER / PRIORITY ENCODER / LOGICAL SHIFTER / SHIFT REGISTER / LOGICAL</u> <u>SHIFTER Extraction :</u> constraints enable or disable corresponding macro inference.

• Following table indicates how various constraints control the way, the macro-generator implements the inferred various macros:-

| HDL Options                                                                                                                           | Allowed Values                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAM Style                                                                                                                             | Auto/Block/Distributed/Pipe-Distributed RAM                                                                                                                                                                                                                                                                |

| ROM Style                                                                                                                             | Auto/Block/Distributed ROM                                                                                                                                                                                                                                                                                 |

| MUX Style                                                                                                                             | Auto/MUXF/MUXCY (Value AUTO indicates that XST looks for best implementation for each macro inference)                                                                                                                                                                                                     |

| Multiplier Style                                                                                                                      | Auto/Block/LUT/Pipe_Block/KCM/CSD/Pipe_LUT                                                                                                                                                                                                                                                                 |

| FSM Style                                                                                                                             | BRAM/LUT ; [ Large FSMs can be made more compact and faster by implementing them in Block RAM resources (instead of LUTs) provided in Virtex and later technologies].                                                                                                                                      |

| <b>Case Implementation Style</b><br>( <i>This option instructs XST</i><br><i>how to interpret Verilog Case</i><br><i>statements</i> ) | <ul> <li>None/Full/Parallel/Full-Parallel</li> <li>[ - If <i>full</i> is used, XST assumes that the case statements are complete and avoids latch creation.</li> <li>- If <i>parallel</i> is used, XST assumes that the branches cannot occur in parallel and does not use a priority encoder.]</li> </ul> |

| <b>FSM Encoding Algorithm</b><br>( <i>This constraint selects FSM</i><br><i>encoding technique to use</i> )                           | Auto/One-Hot/Compact/Sequential/Gray/Johnson/Speed1/User<br>(FPGA State Machines are usually One-Hot encoded.)                                                                                                                                                                                             |

## Synthesizing Design – Understanding HDL Options

*For e.g. In Shift Add Multiplier Synthesis, leaving FSM Encoding Algorithm as "Auto" causes One-Hot encoding to be implemented for* <cur\_state> *and* <nxt\_state> *signal.*

Using one-hot encoding for signal <cur\_state>.

INFO:Xst:2117 - HDL ADVISOR - Mux Selector <cur\_state> of Case statement line 121 was re-encoded using one-hot encoding. The case statement will be optimized (default statement optimization), but this optimization may lead to design initialization problems. To ensure the design works safely, you can:

- add an 'INIT' attribute on signal <cur\_state> (optimization is then done without any risk)

- use the attribute 'signal\_encoding user' to avoid onehot optimization

use the attribute 'safe\_implementation yes' to force XST to perform a safe (but less efficient) optimization Using one-hot encoding for signal <nxt\_state>.

- <u>Safe Implementation</u>: constraint implements FSM with additional logic, that forces FSM to a valid state (recovery state), if FSM gets into an invalid state.

- <u>XOR Collapsing</u>: controls collapsing of cascaded XORs into single XOR.

- <u>*Resource Sharing*</u> constraint enables or disables resource sharing of arithematic operators.

## Synthesizing Design – Understanding Xilinx Options

[Source: Xilinx Synthesis and Simulation Design Guide]

- <u>Add I/O Buffers</u>: enables or disables I/O buffer insertion, to all the port names in the top level entity of the design

- <u>Max Fanout</u>: constraint limits the fanout of nets or signals. Large fanouts can cause routability problems, therefore XST tries to limit fanout by duplicating gates or by inserting buffers. (*These buffers will be protected against logic trimming at the implementation level by defining a KEEP attribute in the NGC file.*)

- <u>Number Of Clock Buffers</u>: controls maximum number of Clock Buffers created by XST.

- <u>Register Duplication</u>: enables or disables register replication, during timing optimization and fanout control.

- *Equivalent Register Removal* : enables or disables removal of equivalent registers, described at the RTL Level.

- <u>*Register Balancing*</u> : option allows to move flip-flops and latches across logic to increase clock frequency.

(Forward Register Balancing will move a set of flip-flops that are at the inputs of a LUT to a single flip-flop at its output. Backward Register Balancing will move a flip-flop which is at the output of a LUT to a set of flip-flops at its inputs.)

- <u>Move First Stage</u> : constraint controls the retiming of registers with paths coming from primary inputs.

- <u>Move Last Stage</u> : constraint controls the retiming of registers with paths going to primary outputs.

- <u>Pack I/O Registers into IOBs</u> : constraint packs flip-flops in the I/Os to improve input/output path timing.

- <u>Slice Packing</u> : option enables the XST internal packer, which attempts to pack critical LUT-to-LUT connections within a slice or a CLB.

- <u>Use Clock Enable</u> : enables or disables the use of clock enable function in flip-flops. The disabling of the clock enable function is typically used for ASIC prototyping on FPGAs. In auto mode, XST tries to estimate a trade off between using a dedicated clock enable input of a flip-flop input and putting clock enable logic on the D input of a flip-flop.

- <u>Use Synchronous Set/Reset</u> : constraint enables or disables the use of synchronous set/reset function in flip-flops.

- *Optimize Instantiated Primitives* : Constraint allows XST to optimize Xilinx library primitives that have been instantiated in HDL.

### Synthesizing Design – Analyzing Synthesis Report

#### • <u>HDL Compilation & Analysis</u>

During HDL Compilation and HDL Analysis, XST parses and analyzes VHDL/Verilog files and gives the name of the libraries into which they are compiled. During this step, XST may report potential mismatches between synthesis and

simulation results, potential multi-sources, and other issues.

| ======================================= |                                |                                                                                           |

|-----------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------|

| *                                       | HDL Compilation                | *                                                                                         |

| Compiling what file                     | //home/ucore/pallavin/multiply | ======================================                                                    |

|                                         |                                | sniit_add_muitipiier_synth/sniit_add_muitipiier/sniit_add_muitipiier.vnd in Library work. |

| *                                       | HDL Analysis                   | *                                                                                         |

|                                         |                                |                                                                                           |

Analyzing Entity <shift\_add\_multiplier> in library <work> (Architecture <shift\_add\_multiplier\_logic>). Entity <shift\_add\_multiplier> analyzed. Unit <shift\_add\_multiplier> generated.

#### • HDL Synthesis

During this step, XST tries to recognize as many basic macros as possible ,to create a technology specific implementation.

HDL Synthesis \_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_\_ Performing bidirectional port resolution... Synthesizing Unit <shift\_add\_multiplier>. Related source file is "/home/users/pallavip/multiply/shift\_add\_multiplier\_synth/shift\_add\_multiplier/shift\_add\_multiplier.vhd" Using one-hot encoding for signal <cur\_state>. Using one-hot encoding for signal <nxt\_state>. WARNING:Xst - Property "use\_dsp48" is not applicable for this technology. Found 1-bit register for signal <mul\_done\_o>. Found 1-bit register for signal <mul\_rdy\_o>. Found 3-bit register for signal <cur\_state>. Found 64-bit register for signal <mul1\_shift\_reg>. Found 32-bit register for signal <mul2\_shift\_reg>. Found 64-bit register for signal <product\_d1>. Found 64-bit adder for signal <product\_d1\$addsub0000> created at line 174. Summary: inferred 162 D-type flip-flop(s). inferred 1 Adder/Subtractor(s). Unit <shift\_add\_multiplier> synthesized.

### Synthesizing Design – Analyzing Synthesis Report

Following is the sectional details of Synthesis Report (.syr) file :-

• <u>Advanced HDL Synthesis</u> : During this step, XST performs advanced macro recognition and inference like recognizing dynamic shift registers, implementing pipelined multipliers, coding state machines, etc.

(Following is the Advanced Synthesis Report section generated for Shift & Add Multiplier)

|\_\_\_\_\_\_ Advanced HDL Synthesis \_\_\_\_\_\_ Loading device for application Rf\_Device from file '3s500e.nph' in environment /cad/Xilinx. Advanced HDL Synthesis Report Macro Statistics # Adders/Subtractors : 1 64-bit adder : 1 # Registers : 165 Flip-Flops : 165 Final Results *Low Level Synthesis* : During this step XST RTL Top Level Output File Name : shift\_add\_multiplier.ngr Top Level Output File Name : shift\_add\_multiplier **Output Format** : NGC reports the potential removal of equivalent Optimization Goal : Speed Keep Hierarchy : NO flip-flops, register replication, etc Design Statistics # IOs : 133 Cell Usage : 643 # BELS *Final Report* : includes (*NGC*) output file name GND 1 LUT2 104 # (having extension .ngr), target family and cell usage. LUT3 20 # LUT4 256 # MUXCY 71 # MUXF5 127 # VCC 1 # XORCY : 63 165 # FlipFlops/Latches FDC 164 FDP 1 # Clock Buffers 1

BUFGP

OBUE

IO Buffers IBUF 1

132

66

: 66

÷ .

#

#

#

### Synthesizing Design – Analyzing Synthesis Report

Final Report also includes following information :-

• <u>Device Utilization Summary</u>: where XST estimates the number of slices, gives the number of flip-flops, IOBs, BRAMS, etc. This report is very close to the one produced by MAP.

Following is the Device Utilization Summary & Clock Information for Shift Add Multiplier Synthesis :

| Device utilization summary:     |     |        |      |              | Clock Information:                  |                 |      |

|---------------------------------|-----|--------|------|--------------|-------------------------------------|-----------------|------|

| Selected Device : 3s500epq208-5 |     |        |      | Clock Signal | Clock buffer(FF name)               | Load            |      |

|                                 |     |        |      |              | clk_i                               | BUFGP           | 165  |

| Number of Slices:               | 198 | out of | 4656 | 4%           |                                     | +               | ++   |

| Number of Slice Flip Flops:     | 165 | out of | 9312 | 1%           | Asynchronous Control Signals Inform | ation           |      |

| Number of 4 input LUTs:         | 380 | out of | 9312 | 4%           |                                     |                 |      |

| Number of IOs:                  | 133 |        |      |              |                                     | +               | ++   |

| Number of bonded IOBs:          | 133 | out of | 158  | 84%          | Control Signal                      | Buffer(FF name) | Load |

| Number of GCLKs:                | 1   | out of | 24   | 4%           | rst_i                               | +<br>  IBUF     | 165  |

|                                 |     |        |      |              |                                     | +               | ++   |

- <u>*Clock Information:*</u> gives information about the number of clocks in the design, how each clock is buffered and how many loads it has.

- <u>*Timing report*</u>: Timing Summary section gives a summary of following timing paths :-

- (i) The path from any clock to any clock (*i.e. flop to flop delay*) in the design:

- (ii) The maximum path from all primary inputs to the sequential elements.

- (iii) The maximum path from the sequential elements to all primary outputs.

- (iv) The maximum path from input to output pad.

Timing Summary for Shift Add Multiplier Synthesis ->

Timing Summary: \_\_\_\_\_ Speed Grade: -5

> Minimum period: 7.295ns (Maximum Frequency: 137.079MHz) Minimum input arrival time before clock: 5.269ns Maximum output required time after clock: 4.182ns Maximum combinational path delay: No path found

### Synthesizing Design-Generating Post-Synthesis Simulation Model

### **Requirement & Generation of Post-Synthesis Simulation Model :**

To verify whether the correct functionality of the design is retained, after synthesizing it into netlist; HDL Design's equivalent simulation model can be generated, by clicking on Generate Post-Synthesis Simulation Model option within Synthesis-XST process list. (Netlist simulation model is generated in netgen/synthesis directory)

#### **<u>Post-Synthesis Simulation using Modelsim :</u>**

Post-Synthesis Simulation Model can be compiled & simulated using the same HDL testbench, that was used for HDL behavioral code verification.

In Modelsim, after creating a new project for Post Synthesis Simulation, include Netlist (\_synthesis.vhd) from <ise\_project>/netgen/synthesis directory. This netlist file is compiled along with testbench, instead of HDL behavioral Code being compiled.

#### **Post-Synthesis Simulation Result :**

For the generated Post-Synthesis Simulation Model, no standard delay file (.sdf file) is back-annotated during simulation.(*Thus, UNISIM Library primitives, included in the synthesis generated netlist, do not have any delay associated with it*)

Therefore, expected Post-Synthesis Simulation result is same as Functional Verification result of HDL Design, as can be seen in following Post-Synthesis simulation waveform for Shift-Add Multiplier design :-

| ↓r_tb:mul1:clk_i  | 0                          |      |         |   |                                         |       |                   |         |        |                     |

|-------------------|----------------------------|------|---------|---|-----------------------------------------|-------|-------------------|---------|--------|---------------------|

| 🔷er_tb:mul1:rst_i | 0                          |      |         |   |                                         |       |                   |         |        |                     |

| 🔷b:mul1:data1_i   | 00001011                   | 00 ) | 0000101 | 1 |                                         |       |                   |         |        |                     |

| 🔶b:mul1:data2_i   | 00000111                   | FF 1 | 0000011 | 1 |                                         |       |                   |         | ĺ      |                     |

|                   |                            |      |         |   |                                         |       |                   |         |        |                     |

|                   | 0000000000112221           |      |         |   | 000000000000000000000000000000000000000 | 01011 | 00000000          | 0011121 | (00000 | DO X0000000         |

|                   | 0000000000112221<br>1      |      |         |   | 000000000000000000000000000000000000000 | 01011 | ,000000000        | 0011121 | 00000  | 00 <u>(</u> 0000000 |

| ♦ul1:product_o    | 0000000000112221<br>1<br>1 |      |         |   | 000000000000000000000000000000000000000 | 01011 | <u>(000000000</u> | 0011121 | 00000  | <u>DO (0000000</u>  |

### Specifying User Constraints

#### <u>Need for Setting Constraints</u> :

For Design to meet desired Area/Frequency Specification on FPGA, it is required to tell the Implementation Tool for what performance it should optimize the design implementation processes like Map, Place & Route. Thus, User Defined Constraints allows to specify desired Clock period/ Pad to Setup/Clock to Pad delay & assign areas to hierarchical blocks of logic.

Physical User Constraint also allows to allocate HDL design's I/O signals to specific package pins.

#### Adding Constraints to Design :

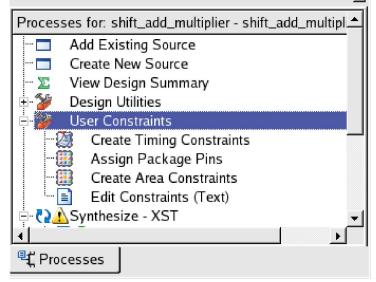

User can specify Constraints for ISE Design Project, either through GUI by double-clicking on following options available within *User Constraints* label in *Processes* Window:-

- (i) Create Timing Constraints

- (ii) Assign Package Pins

- (iii) Create Area Constraints

(or) the User can specify constraints in .**ucf** file, through any text editor.

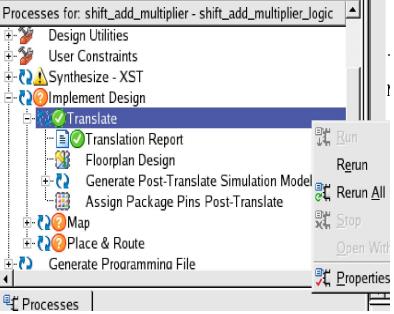

While opening Constraint Editor window, Translate step runs automatically because implementation stage must see the netlist before it can offer the user the chance to constraint sections of design.

## Specifying User Constraints – Timing Constraints

### (i) <u>Timing Constraints :</u>

The <u>Global Clock Domain and Input/Output Ports</u> tab of Create Timing Constraints window automatically displays all clock nets in the design, and enables designer to define the associated Period, Pad to Setup, and Clock to Pad values.

| 🕸 Xilinx Constraints Editor                                                                                                                             |              |                |                              |                   |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|------------------------------|-------------------|--|--|--|--|--|--|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>W</u> indow <u>H</u> elp                                                                                      |              |                |                              |                   |  |  |  |  |  |  |

| 🗋 🔌 🗟  🗙 🕮 印 🤌 😪                                                                                                                                        |              |                |                              |                   |  |  |  |  |  |  |

| Se Global*                                                                                                                                              |              |                |                              |                   |  |  |  |  |  |  |

| Clock Net Name Period Pad to Setup Clock to Pad                                                                                                         | Port Name 🛛  | Port Direction | Pad to Setup                 | Clock to Pad      |  |  |  |  |  |  |

| clk_i 7.5 ns HIGH 50 % 2 ns 2 ns                                                                                                                        | data2_i<6>   | INPUT          |                              | N/A               |  |  |  |  |  |  |

|                                                                                                                                                         | data2_i<7>   | INPUT          |                              | N/A               |  |  |  |  |  |  |

|                                                                                                                                                         | data2_i<8>   | INPUT          |                              | N/A               |  |  |  |  |  |  |

|                                                                                                                                                         | data2_i<9>   | INPUT          |                              | N/A               |  |  |  |  |  |  |

| ▲                                                                                                                                                       | mul_done_o   | OUTPUT         | N/A                          |                   |  |  |  |  |  |  |

|                                                                                                                                                         | mul_rdy_o    | OUTPUT         | N/A                          |                   |  |  |  |  |  |  |

| Pad to Pad                                                                                                                                              | product_o<0> | OUTPUT         | N/A                          |                   |  |  |  |  |  |  |

|                                                                                                                                                         | product o<1> |                | N/A                          |                   |  |  |  |  |  |  |

| XI NET "clk_i" TNM_NET = "clk_i";<br>TIMESPEC "TS_clk_i" = PERIOD "clk_i" 7.5 ns HIGH 50 %; → Syntax fo<br>OFFSET = IN 2 ns BEFORE "clk_i"; → Syntax fo |              | raint<br>raint | as an alternative to using ( | Constraint Editor |  |  |  |  |  |  |

(Since, there are no combinatorial paths in Shift Add Multiplier design, Pad to Pad constraint is not specified for this case.)

ISE tool Timing Analyzer is used to analyze the results of these timing specifications for the design.

### Specifying User Constraints – Timing Constraints

[Source: Xilinx Timing Constraint User Guide]

<u>Clock Period</u> constraint ensures that the internal paths starting and ending at synchronous points (Flip-Flops /RAM / Latches ) have logic delay less than Maximum Delay allowed in the design specification.

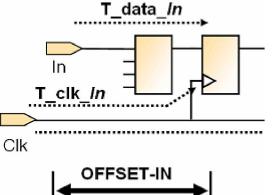

<u>**Pad to Setup**</u> is the path starting at Input Port of the design and ending at an input to a flip-flop/latch/RAM—wherever there is a setup time against a control signal.

The Pad to Setup constraint defines the maximum time required for the data to enter the FPGA, travel through logic and routing, and arrive at the input before the clock or control signal arrives.

<u>Pad-to-Setup</u> Delay Constraint can be calculated as follows :-

where,  $T_{Data}$  = Total Data path delay from the Flip Flop  $T_{Setup}$  = Intrinsic Flip Flop setup time  $T_{Clock}$  = Total Clock path delay to the Flip Flop  $T_{Offset_IN\_BEFORE}$  = Overall Setup Requirement

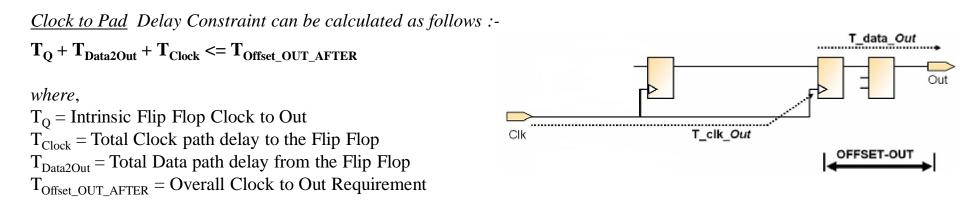

<u>Clock to Pad</u> is the path starting at the Q output of a flip-flop or latch and ending at Output Port of the design. It includes the Clock-to-Q delay of the flip-flop and path delay from that flip-flop to FPGA output.

The Clock to Pad constraint defines the maximum time required for the data to leave the source flip-flop, travel through logic and routing, and arrive at output pin of FPGA.

The clock-to-pad path time is the maximum time required for the data to leave the source flip-flop, travel through logic and routing, and leave the chip.

### Specifying User Constraints – *Timing Constraints*

[Source : Xilinx Timing Constraint User Guide]

<u>Pad to Pad</u> constraint constraints combinatorial asynchronous paths having start and endpoints as Pads of the design.

## Specifying User Constraints – Assigning Package Pins

#### (ii) Assigning Package Pins :

Package Pins can be assigned to Design's Input/Output Ports through *LOC* constraint in **.ucf** file or through **Assign Package Pin** GUI Window.

| ×      | Xilinx PACE - /ho                      | me/users/pallavi   | ip/mult     | iply/shift_       | add_ | _m | ultiplier_syr      | nth1/shift_a | dd_multiplier/shi | ift_add_multi    | i 📃                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 🕻 s          | hift_ad      | ld_multi      | plier.        | ucf ( | ~/mult          | iply/s      |

|--------|----------------------------------------|--------------------|-------------|-------------------|------|----|--------------------|--------------|-------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|---------------|---------------|-------|-----------------|-------------|

| F      | <u>-</u> ile <u>E</u> dit <u>V</u> iew | IOBs <u>A</u> reas | <u>T</u> oo | ols <u>W</u> indo | w    | He | elp                |              |                   |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <u>F</u> ile | <u>E</u> dit | <u>T</u> ools | <u>S</u> ynta | ax    | <u>B</u> uffers | <u>W</u> in |

|        | ) 🖻 🖬 🎒 🕨                              | o 🕺 🧩 🎗            | ₽           | St 📃 🗌            | ×    | 2  | 3 🔝 🚮              | <b>n 1</b>   | 🖪 🔤 🗖 💥 G         | Q @ ¥ Q          | Image: Control of the second secon | Ø            |              | ] 🔤           | \$            | è     |                 | <b>b</b> (  |

| -      | _ D                                    | esign Browser      |             |                   |      | -  | P                  | Package Pin: | s for xc3s500e-5  | 5 <b>-pq</b> 208 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NET          | "prod        | luct_o<       | (49>"         | LOC   | -               | .85:        |

| Ī      | ≞ 🗟 I/O Pins                           |                    |             |                   | Ī    |    |                    | 0            |                   |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NET          | "prod        | luct_o<       | :54>"         | LOC   | = P1            |             |

|        | Global Logi                            | С                  |             |                   |      |    | Pir                | in Name: "P1 | " Pin Type: "PR(  | OG_B"            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <u>N</u> ET  | "data        | 12_i<6>       | " LO          | C =   | P12;            |             |

|        |                                        |                    |             |                   |      |    |                    |              |                   |                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |              |               |               |       |                 |             |

| r<br>L | – Design                               | Object List – I/C  | ) Pins      |                   |      |    |                    |              |                   |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |              |               |               |       |                 |             |

| Г      | I/O Name                               | I/O Direction      | _           | Bank              | Ā    |    |                    |              |                   |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |              |               |               |       |                 |             |

| ŀ      | clk_i                                  | Input              | P18         | BANKO             |      |    | 8                  |              |                   |                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |              |               |               |       |                 |             |

|        | data1_i<0>                             | Input              | P43         | BANK3             |      |    | 8                  |              | Top View          |                  | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |              |               |               |       |                 |             |

|        | data1_i<1>                             | Input              | P19         | BANKO             | 111  |    | 8                  |              |                   |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |              |               |               |       |                 |             |

|        | data1_i<2>                             | Input              | P81         | BANK2             |      |    |                    |              |                   |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |              |               |               |       |                 |             |

|        | data1_i<3>                             | Input              | P91         | BANK2             | 111  |    |                    |              |                   |                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |              |               |               |       |                 |             |