# **EINSTEIN COLLEGE OF ENGINEERING** Sir.C.V.Raman Nagar, Tirunelveli-12

## Department of Electrical and Electronic Engineering.....

Subject Code: EE37

Subject Name : Electron Devices and Circuits lab

| Name            | : |

|-----------------|---|

| Reg No          | : |

| Branch          | : |

| Year & Semester | : |

## LIST OF EXPERIMENTS

| S.NO | EXPERIMENTS                                                                                           | PAGE.NO |

|------|-------------------------------------------------------------------------------------------------------|---------|

| 1    | Characteristics of PN junction diode and Zener diode                                                  |         |

| 2    | Characteristics of Transistor under common emitter,<br>common collector and common base configuration |         |

| 3    | Characteristics of JFET                                                                               |         |

| 4    | Characteristics of UJT                                                                                |         |

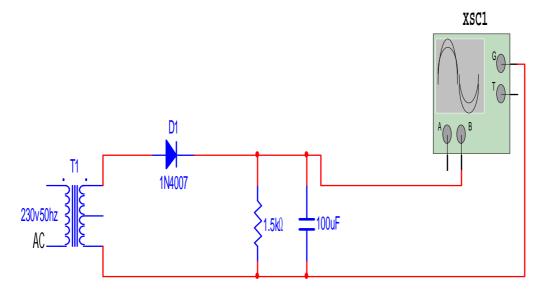

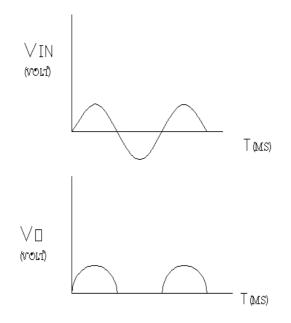

| 5    | Characteristics of SCR, DIACA and TRIAC                                                               |         |

| 6    | Single phase half wave and full wave rectifiers with inductive and capacitive filters                 |         |

| 7    | Differential amplifier using FET                                                                      |         |

| 8    | Series and parallel resonance circuits                                                                |         |

| 9    | Realization of Passive filters                                                                        |         |

| 10   | Characteristics of photo diode, photo transistor                                                      |         |

| 11   | Study of CRO                                                                                          |         |

## **INDEX**

| Expt.<br>No. | Expt.<br>Date | Name of the Experiment | Marks | Staff<br>Signature |

|--------------|---------------|------------------------|-------|--------------------|

|              |               |                        |       |                    |

|              |               |                        |       |                    |

|              |               |                        |       |                    |

|              |               |                        |       |                    |

|              |               |                        |       |                    |

|              |               |                        |       |                    |

|              |               |                        |       |                    |

|              |               |                        |       |                    |

|              |               |                        |       |                    |

|              |               |                        |       |                    |

| L | 1 | 1 |  |

|---|---|---|--|

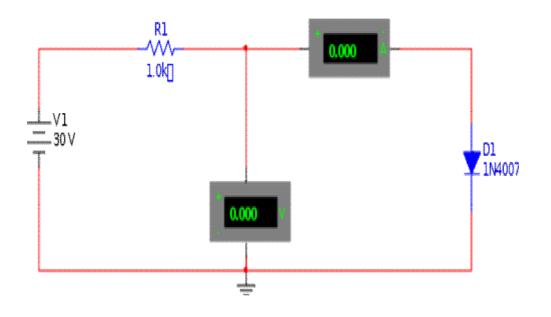

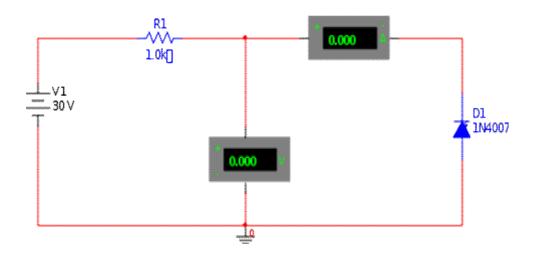

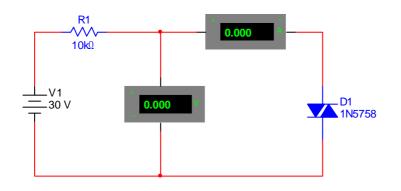

## **CIRCUIT DIAGRAM:**

## **DIODE FORWARD BIASING**

## **DIODE REVERSE BIASING**

## Ex. No: CHARACTERISTICS OF PN JUNCTION DIODE

#### Date:

#### AIM:

To draw the VI characteristics of PN Junction diode and find the parameters.

#### **APPARATUS REQUIRED:**

| S.No. | Apparatus required | Range      | Quantity    |

|-------|--------------------|------------|-------------|

| 1.    | RPS                | (0-30)V    | 1           |

| 2.    | Voltmeter          | (0-2)V     | 1           |

|       |                    | (0-30)V    | 1           |

| 3.    | Ammeter            | (0-100)mA. | 1           |

|       |                    | (0-500)µA  | 1           |

| 4.    | Resistor           | 1ΚΩ        | 1           |

| 5.    | Diode              | IN 4007    | 1           |

| 6.    | Bread Board        |            | As required |

| 7.    | Connecting wires   |            | As required |

## FORMULAE USED:

## FOR DIODE:

- (1) Diode forward resistance,  $R_f = \Delta V_{f/} \Delta I_f$

- (2) Reverse saturation current,  $I_o = I / (exp (V/\eta V_T)-1)$

- (3) Reverse resistance,  $R_r = \Delta V_r / \Delta I_r$

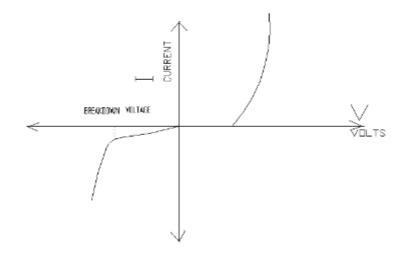

## **V-I Characteristics of Diode**

## **TABULATION:**

## FORWARD BIAS

## **REVERSE BIAS**

| $V_{f(V)}$ | I <sub>f</sub> (mA) |  |

|------------|---------------------|--|

|            |                     |  |

|            |                     |  |

|            |                     |  |

|            |                     |  |

|            |                     |  |

|            |                     |  |

|            |                     |  |

|            |                     |  |

|            |                     |  |

|            |                     |  |

| V <sub>r</sub> (v) | $I_r(\mu A)$ |

|--------------------|--------------|

|                    |              |

|                    |              |

|                    |              |

|                    |              |

|                    |              |

|                    |              |

|                    |              |

|                    |              |

|                    |              |

|                    |              |

|                    |              |

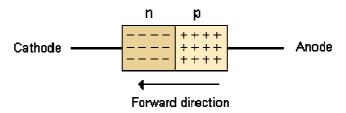

#### **THEORY:**

Diode is a simplest bipolar semiconductor component. It consists of two regions. One region is doped heavily with N type material. So it is called as N region. So it is denoted as cathode. Similarly, other region is doped heavily with P type material. It is called as P region. So it is denoted as anode. It is shown in fig:

#### **PRINCIPLE OF OPERATION:**

#### FORWARD BIAS:

The diode is said to be forward biased, when anode is connected to the positive terminal of DC source, the holes in the P region of the diode are repelled by the positive current. Hence these holes have sufficient energy to cross the potential barrier at the PN junction. Similarly as the cathode is connected to negative terminal of the DC source. So the electrons in the N region are repelled by the applied voltage. Hence they also get sufficient energy to cross the junction. So the potential barrier at the junction becomes zero. So the diode acts as ordinary resistor with a small resistance because of internal voltage drop in it..

#### **REVERSE BIAS:**

Similarly when the anode is connected to the negative terminal of the DC source, the diode is said to be reverse biased. In this case, the current from the source is in such a way that, it attracts the holes towards the negative terminal and electrons towards the positive terminal connected to cathode of the diode. So this causes the potential barrier at the junction to increase a lot. During reverse bias the diode acts almost as a open circuit. **MODEL CALCULATION:**

During reverse bias small current flows through it. This current is called as reverse saturation current ( $I_o$ ). When voltage is increased the electric field in the junction increases. This increases the reverse saturation current. At particular voltage, small increases in voltage, current increases large rate. This is called as **avalanche breakdown**.

#### **CUT IN VOLTAGE:**

Even though voltage is applied to the diode during forward bias, initially there is no current flowing through the diode till a particular forward voltage is applied. The forward voltage at which the diode current starts to increase is called as **cut-in voltage.** For silicon 0.7V, for germanium 0.3V.

#### **PROCEDURE:**

#### FORWARD CHARACTERISTICS:

- 1. Connections are made as per the circuit diagram.

- 2. Keep the RPS in minimum value and switch ON the power supply.

- 3. Gradually increase the forward voltage in step by step of variation, Note down the forward voltage and current values and graph is plotted.

#### **REVERSE CHARACTERISTICS:**

- 1. Connections are made as per the circuit diagram.

- 2. Keep the RPS in minimum value and switch ON the power supply.

- 3. Gradually increase the reverse voltage in step by step of variation, Note down the reverse voltage and current values and graph is plotted.

The characteristics of diode are drawn between Voltage and Current with forward characteristics on **first quadrant** and reverse characteristics on **third quadrant**.

**RESULT:**

#### **DISCUSSION QUESTIONS:**

#### 1. What is semiconductor material? How does it differ from a conductor?

A semiconductor is a material whose conductivity lies somewhere between that of a conductor and insulator. The typical value of conductivity is  $100\Omega/cm^3$ . Germanium and silicon are most commonly used as semiconductor materials.

#### 2. Why do we prefer extrinsic semiconductor than intrinsic semiconductors?

Extrinsic semiconductor has high electrical conductivity which depends on the number of doping atoms and has high operating temperature. But in the intrinsic semiconductor the electrical conductivity is very small and is not a constant at different temperature.

#### 3. Define the term drift current?

When an electrical field is applied across the semiconductor, the holes move towards the negative terminal of the battery and electrons more towards the positive terminal of the batter. This combine effect causes a current flow in the circuit. This current is called as drift current.

#### 4. Define the term diffusion current?

Diffusion current is due to the movement of charge carriers by concentration gradients of charges by applied electrified d strength.

## 5. What is PN junction diode?

A PN junction diode is a two terminal device consisting of a PN junction formed either in germanium or silicon crystal. A PN junction is formed from a piece of semiconductor by diffusing P-type material to one half sides and N type material to other half side.

## 6. What is depletion region in a PN junction diode?

The region around the junction from which the charge carriers are depleted is called as depletion region. When a PN junction is forward biased, the depletion region width decreases

When a PN junction is reversed biased the depletion region width increase.

## 7. Define the term transition capacitance $C_T$ of a diode?

When a PN junction is reverse biased the depletion layer acts like a dielectric material while P and N type region on either side have low resistance acts as the plates. In reverse biased PN junction may be regarded as parallel plate capacitor. This

junction capacitance is called transition capacitance. It is denoted by  $C_T$  and is also called as space charge capacitance or depletion layer capacitance.

#### 8. Explain the terms knee voltage and breakdown voltage w.r.t. diodes?

Knee voltage: the forward voltage at which the current through the PN junction starts increasing rapidly. It is also called as cut in voltage.

Breakdown voltage: the reverse voltage at which the PN junction breakdown occurs is called as breakdown voltage.

## 9. List the application of PN junction diode?

- Used as rectifier diodes in dc power supplies

- Used as signal diodes in communication circuits for modulation and demodulation

- Used in clipped and clamper circuits

- Used as a switch in logic circuits used in computers

## 10. What is avalanche breakdown in PN junction diode?

The avalanche breakdown takes place when both sides of the junction are lightly doped and consequently the depletion layer is large. When the reverse bias voltage is increased the accelerated free electrons collide with the semiconductor atoms in the depletion region. Due to the collision with valance electrons, covalent bonds are broken and electron hole pairs are generated. These new charges carriers so produced acquire energy from applied potential and in turn produced additional carriers. This forms cumulative process is called avalanche multiplication it causes the reverse current increase rapidly. This leads to avalanche breakdown. Once this breakdown occurs, the junction cannot regain its original position.

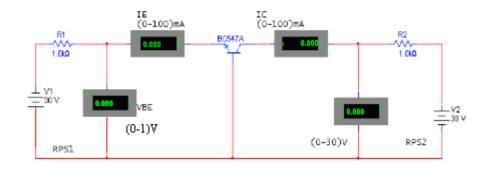

## CIRCUIT DIAGRAM FOR COMMON BASE CONFIGURATION

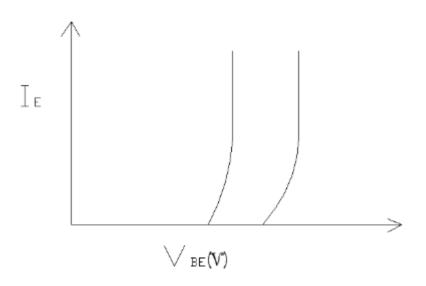

## CHARACTERISTICS OF CB CONFIGURATION:

## INPUT CHARACTERISTICS

# Ex.No: CHARACTERISTICS OF COMMON BASE CONFIGURATION

## Date: AIM:

To determine the characteristics of BJT under Common base configuration.

## **APPARATUS REQUIRED:**

| S.No. | Apparatus required | Range     | Quantity    |

|-------|--------------------|-----------|-------------|

| 1.    | RPS                | (0-30)V   | 2           |

| 2.    | Voltmeter          | (0-1)V    | 1           |

|       |                    | (0-10)V   | 1           |

| 3.    | Ammeter            | (0-500)µA | 1           |

|       |                    | (0-100)mA | 1           |

| 4.    | Resistance         | 1ΚΩ       | 2           |

| 5.    | Transistor         | BC 107    | 1           |

| 6.    | Bread board        |           | As required |

| 7.    | Connecting wires   |           | As required |

## FORMULA USED:

- (1) Input impedance  $h_{ib} = \Delta V_{EB} / \Delta I_E$ , with  $V_{CB}$  constant

- (2) Output conductance  $\,h_{ob}\,=\,\Delta I_c\,/\,\Delta\,V_{CB}\,$  , with  $\,$   $I_E$  constant

- (3) Forward current gain  $h_{fb}$  =  $\Delta I_c$  /  $\Delta I_E,~$  with  $V_{CB}$  constant

- (4) Reverse Voltage gain  $h_{rb}~=~\Delta~V_{EB}~/\Delta~V_{CB}$  , with  $~I_{E}~$  constant

## THEORY:

A Bipolar Junction Transistor (BJT) is a three terminal device in which the operation depends on the interaction of both majority and minority carriers. The three terminals are Base, Emitter and collector. The arrow on the emitter specifies the direction of current flow when the EB junction is forward biased. Emitter is heavily doped; it can inject large number charge carriers into to the base. Base is lightly doped and very thin. It passes most of the injected charge carriers from the emitter into the collector. Collector is moderately doped.

## **OUTPUT CHARACTERISTICS**

## TABULATION FOR CB CONFIGURATION: INPUT CHARACTERISTICS

|       | V <sub>CB</sub> =  |                    | $V_{CB} = V$       |                    | V <sub>CB</sub> = v |                    |

|-------|--------------------|--------------------|--------------------|--------------------|---------------------|--------------------|

|       | V <sub>BE(V)</sub> | I <sub>E(mA)</sub> | V <sub>BE(V)</sub> | I <sub>E(mA)</sub> | V <sub>BE(V)</sub>  | I <sub>E(mA)</sub> |

| ····· |                    |                    |                    |                    |                     |                    |

|       |                    |                    |                    |                    |                     |                    |

|       |                    |                    |                    |                    |                     |                    |

|       |                    |                    |                    |                    |                     |                    |

|       |                    |                    |                    |                    |                     |                    |

|       |                    |                    |                    |                    |                     |                    |

#### **PRINCIPLE OF OPERATION:**

This is also grounded Base Configuration. Emitter is the input terminal, Collector is the output terminal and Base is the common terminal.

#### **INPUT CHARACTERISTICS:** I<sub>E</sub> Vs V<sub>EB</sub> constant V<sub>CB</sub>

The collector base voltage  $V_{CB}$  is kept constant at zero volt and emitter current  $I_E$  is increased from zero in suitable equal steps by increasing  $V_{EB}$ . This is repeated for higher fixed values of  $V_{CB}$ . When  $V_{CB}$  is equal to zero then the emitter-base junction is get forward biased and the junction behaves as a forward biased diode, so that the emitter current  $I_E$  increases rapidly with small increase in emitter base voltage  $V_{EB}$ . When  $V_{CB}$  is increased keeping  $V_{EB}$  constant, the width of the base region will decrease.

#### **OUTPUT CHARACTERISTICS:** I<sub>C</sub> Vs V<sub>CB</sub> constant I<sub>E</sub>

The emitter current IE is kept constant at a suitable value by adjusting the emitter base voltage  $V_{EB}$ . Then  $V_{CB}$  increased in suitable equal steps and collector current  $I_C$  is noted for each value of  $I_E$ . This is repeated for different fixed values of  $I_E$ .

#### **PROCEDURE:**

#### **Input characteristics:**

- 1. Keeping the voltage across collector to emitter ( $V_{CE}$ ) as constant, tabulate the values of base current for various values of base emitter voltage ( $V_{BE}$ .).

- $_{\rm 2.}$  Repeat the same procedure for various values of  $V_{\rm CE.}$

#### **Output characteristics:**

- 1. Keeping the base current as constant, tabulate the values of collector current  $(I_C)$  for various values of collector emitter voltage ( $V_{CE}$ ).

- 2. Repeat the same procedure for various constant values of base current (I<sub>B</sub>).

| I <sub>E =</sub>   | mA                 | $I_{E}=$ | mA                 | $I_{E=}$ |                    |

|--------------------|--------------------|----------|--------------------|----------|--------------------|

| V <sub>BC(V)</sub> | I <sub>C(mA)</sub> |          | I <sub>C(mA)</sub> |          | I <sub>C(mA)</sub> |

|                    |                    |          |                    |          |                    |

|                    |                    |          |                    |          |                    |

|                    |                    |          |                    |          |                    |

|                    |                    |          |                    |          |                    |

|                    |                    |          |                    |          |                    |

|                    |                    |          |                    |          |                    |

|                    |                    |          |                    |          |                    |

|                    |                    |          |                    |          |                    |

|                    |                    |          |                    |          |                    |

|                    |                    |          |                    |          |                    |

## **OUTPUT CHARACTERISTICS**

MODEL CALCULATION:

**RESULT:**

## **DISCUSSION QUESTIONS:**

## 1. What is bipolar junction transistor?

A bipolar junction transistor (BJT) is a three terminal semiconductor device in which the operation depends on the interaction of both majority and minority carriers and hence the name bipolar.

## 2. What are the different configurations of BJT?

- Common emitter configuration

- Common collector configuration

- Common base configuration

## 3. What is thermal runaway?

The continuous increase in collector current due to poor biasing causes the temperature at collector terminal to increase. If no stabilization is done, the collector leakage current also increases. This further increases the temperature. This action becomes cumulative and ultimately the transistor burns out. The self destruction of an unstabilised transistor is known as thermal runaway.

## 4. Define the different operating region of transistor?

Active region: The collector junction is reverse biased and emitter junction is forward biased.

Cut off region: The collector and emitter junction are both reverse biased.

Saturation region: The collector and emitter junction are forward biased.

## 5. List the uses of emitter follower (common collector configuration) circuit?

- It is widely used in electronic instruments because of low output impedance and high input impedance.

- It is used of impedance matching.

## 6. Define alpha and beta of the transistor?

The ratio of change in collector current  $I_C$  to the change in emitter current  $I_E$  at constant collector base voltage  $V_{CB}$

$$\alpha = \mathbf{I}_{\mathbf{C}} / \mathbf{I}_{\mathbf{E}}$$

## Base current amplification factor (β)

The ratio of change in collector current  $I_{C}% ^{\prime}(t)$  to the change in base current

$\mathbf{I}_{\mathrm{B}}$

$$\beta = I_C / I_B$$

#### 7. What is meant by early effect?

When the collector base voltage is made to increase, it increase the depletion region across the collector base junction, with the result that the effective width of base terminal decreases. This variation of effective base width by collector base voltage is known as base width modulation or early effect.

#### 8. Explain the significance of early effect or base width modulation?

It reduces the charges recombination of electron with holes in ht base region, hence the current gain increase with increase in collector base voltage.

The charge gradient is increased within the base; hence the current due to minority carriers across emitter junction increases.

#### 9. Which configuration provides better current gain?

CB configuration

#### 10. What is the significance of $V_{BE}$ and $I_{CO}$ ?

$V_{BE}$  and  $I_{CO}$  are significant because any changes in  $V_{BE}$  and  $I_{CO}$  cause a drastic change in temperature and collector current  $I_{C}$ . It leads to thermal runaway problem.

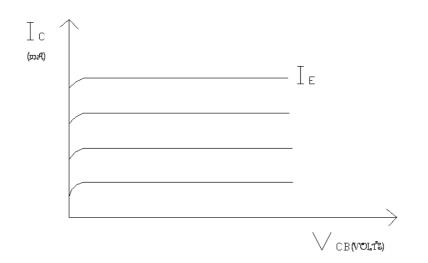

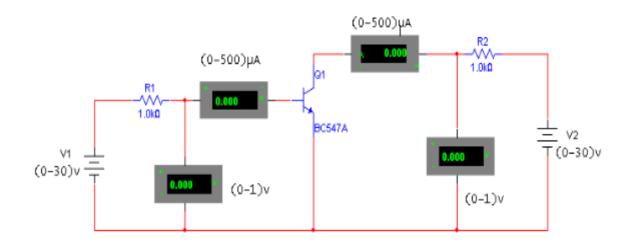

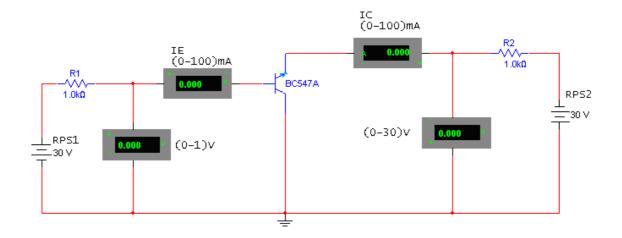

## CIRCUIT DIAGRAM FOR COMMON EMITTER CONFIGURATION:

## MODEL GRAPH FOR CE CONFIGURATION:

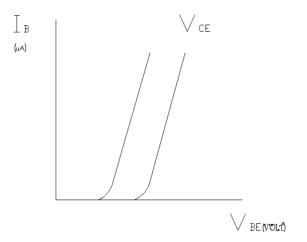

## INPUT CHARACTERISTICS

# Ex.No: CHARACTERISTICS OF COMMON EMITTE CONFIGURATION Date:

## AIM:

To determine the characteristics of BJT under Common Emitter configuration.

#### **APPARATUS REQUIRED:**

| S.No. | Apparatus required | Range     | Quantity    |

|-------|--------------------|-----------|-------------|

| 1.    | RPS                | (0-30)V   | 2           |

| 2.    | Voltmeter          | (0-1)V    | 2           |

| 3.    | Ammeter            | (0-500)µA | 2           |

| 4.    | Resistance         | 1ΚΩ       | 1           |

| 5.    | Transistor         | BC 107    | 1           |

| 6.    | Bread board        |           | 2           |

| 7.    | Connecting wires   |           | As required |

|       |                    |           |             |

|       |                    |           |             |

## FORMULA USED:

- (1) Input impedance hie  $~=\Delta V_{BE}$  /  $\Delta I_B$  , with  $~V_{CE}$  as constant

- (2) Output Admittance  $h_{oe} = \Delta I_c / \Delta V_{CE}$ , with  $I_B$  as constant

- (3) Forward Current gain  $h_{fe} = \Delta I_c / \Delta I_B$ , with  $V_{CE}$  as constant

- (4) Reverse voltage gain  $h_{re} = \Delta V_{BE} / \Delta V_{CE}$ , with  $I_B$  as constant

## **THEORY:**

This is also called grounded emitter configuration. Base is the input terminal, collector is the out put terminal and emitter is the common terminal.

## **OPERATION:**

## Input characteristics:

The collector to emitter voltage is kept constant at zero volt and base current increased from zero in equal steps by increasing  $V_{BE}$ . This procedure is repeated for higher fixed values of  $V_{CE}$  and curves of  $I_B$  Vs  $V_{BE}$  are drawn. When  $V_{CE} = 0$ , the emitter base junction is forward biased and the junction behaves as a

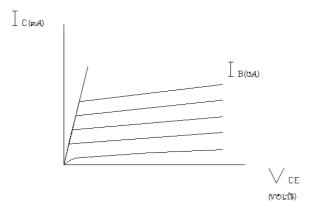

## **OUTPUT CHARACTERISTICS**

| $I_B = \mu A$ $I_B =$ |                     | $\begin{array}{c c} \hline \\ \hline \\ \hline \\ I_B = \mu A \\ \hline \\ I_B = \mu A \\ \hline \\ I_B = \mu A \\ \hline \\ \hline \\ \hline \\ I_B = \mu A \\ \hline \\$ |                     | $I_B = \mu A$      |                     |

|-----------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|---------------------|

| V <sub>CE (V)</sub>   | I <sub>C (mA)</sub> | V <sub>CE (V)</sub>                                                                                                                                                                                                                                        | I <sub>C (mA)</sub> | V <sub>CE(V)</sub> | I <sub>C (mA)</sub> |

|                       |                     |                                                                                                                                                                                                                                                            |                     |                    |                     |

|                       |                     |                                                                                                                                                                                                                                                            |                     |                    |                     |

|                       |                     |                                                                                                                                                                                                                                                            |                     |                    |                     |

|                       |                     |                                                                                                                                                                                                                                                            |                     |                    |                     |

|                       |                     |                                                                                                                                                                                                                                                            |                     |                    |                     |

|                       |                     |                                                                                                                                                                                                                                                            |                     |                    |                     |

|                       |                     |                                                                                                                                                                                                                                                            |                     |                    |                     |

|                       |                     |                                                                                                                                                                                                                                                            |                     |                    |                     |

|                       |                     |                                                                                                                                                                                                                                                            |                     |                    |                     |

|                       |                     |                                                                                                                                                                                                                                                            |                     |                    |                     |

|                       |                     |                                                                                                                                                                                                                                                            |                     |                    |                     |

|                       |                     |                                                                                                                                                                                                                                                            |                     |                    |                     |

|                       |                     |                                                                                                                                                                                                                                                            |                     |                    |                     |

## **OUTPUT CHARACTERISTICS**

forward biased diode. When  $V_{CE}$  increased, the width of the depletion region at the reverse biased collector base junction will increase. Hence the effective width of the base will decrease.

#### **Output characteristics:**

The base current  $I_B$  is kept constant at a suitable value by adjusting base emitter voltage  $V_{BE}$ . The magnitude of collector emitter voltage  $V_{CE}$  is increased in suitable equal steps from zero and the collector current  $I_C$  is noted for each setting  $V_{CE}$ . Now the curves of  $I_C$  versus  $V_{CE}$  are plotted for different constant values of  $I_B$ . Saturation region:

Both junctions are forward biased and an increase in the base current does not cause a corresponding large change in  $I_{C}$ . The ratio of  $V_{CE}$  (sat) to  $I_{C}$  in this region is called saturation resistance.

#### Cut off region:

Both junctions are reverse biased. When the operating point for the transistor enters the cut off region, the transistor is OFF. The transistor is virtually an open circuit between collector and emitter.

#### Active region:

Emitter base junction is forward biased and the collector base junction is reverse biased. If the transistor is to be used as a linear amplifier, it should be operated in the active region.

#### **PROCEDURE:**

#### **Input characteristics:**

- 1. Keeping the voltage across collector to emitter ( $V_{CE}$ ) as constant, tabulate the values of base current for various values of base emitter voltage ( $V_{BE}$ .).

- 2. Repeat the same procedure for various values of  $V_{CE.}$

#### **Output characteristics:**

- 1. Keeping the base current as constant, tabulate the values of collector current  $(I_C)$  for various values of collector emitter voltage ( $V_{CE}$ ).

- 2. Repeat the same procedure for various constant values of base current  $(I_B)$ .

**MODEL CALCULATION:**

**RESULT:**

## **DISCUSSION QUESTIONS:**

## 1. What are the types of breakdown occurs in transistors?

- Avalanche multiplication or avalanche breakdown

- Reach through of punch through

## 2. Why do we prefer silicon for transistor?

Silicon is an indirect band semiconductor the life time of charge carriers is more and hence amplification is more.

## 3. What is meant by stabilization?

The maintenance of the operating point is fixed stable.

## 4. What is the need for biasing?

- To maintain proper zero signal emitter base voltage.

- To maintain proper zero signal collector emitter voltage.

- To maintain proper zero signal collector current.

## 5. What is meant by operating point?

The zero signal values of  $I_C$  and  $V_{CC}$  are known as operating point. It is also called so because the variations of  $I_C$  and  $V_{CC}$  take place about this point when signal is applied. It is also called as Q point and it is the point was the transistor is silent.

## 6. What types of components are used for temperature stabilization?

Passive type of components are used

## 7. What are the types of biasing?

- Fixed bias

- Collector feedback bias

- Self bias or emitter bias

#### 8. Define stability factor?

Stability factor S defined as the rate of change of collector current IC w.r.t reverse saturation current I $\alpha$  keeping  $\beta$  and V<sub>BE</sub> constant.

$S{=}\,\Delta I_C\,/\Delta\,\,I\alpha$

#### 9. What is Q point?

The quiescent operating point is given by the inter section of the bias curve and the dc load line.

#### 10. What is bias? What is the need for biasing?

The proper flow of zero signal collector current and the maintenance of proper collector emitter voltage during the passage of signal is known as transistor biasing.

When a transistor is biased properly, it works efficiently and produces no distortion in the output signal and thus operating point can be maintained stable.

## CIRCUIT DIAGRAM FOR COMMON COLLECTOR CONFIGURATION

# Ex.N CHARACTERISTICS OF COMMON COLLECTOR CONFIGURATION Date:

#### AIM:

To determine the characteristics of BJT under Common collector configuration.

| S.No. | Apparatus required | Range     | Quantity    |

|-------|--------------------|-----------|-------------|

| 1.    | RPS                | (0-30)V   | 2           |

| 2.    | Voltmeter          | (0-1)V    | 2           |

| 3.    | Ammeter            | (0-100)µA | 2           |

| 4.    | Resistance         | 10KΩ      | 1           |

| 5.    | Transistor         | BC 107    | 1           |

| 6.    | Bread board        |           | 2           |

| 7.    | Connecting wires   |           | 1           |

|       |                    |           | As required |

|       |                    |           | As required |

## **APPARATUS REQUIRED:**

## **THEORY:**

This is also called grounded collector configuration. Base is the input terminal, emitter is the out put terminal and collector is the common terminal.

## **OPERATION:**

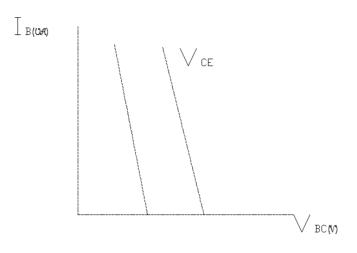

## Input characteristics:

$V_{CE}$  is kept at a suitable fixed value. The base collector voltage  $V_{BC}$  is increase in equal steps and the corresponding increase in I<sub>B</sub> is noted. This is repeated for different fixed values of  $V_{CE}$ .

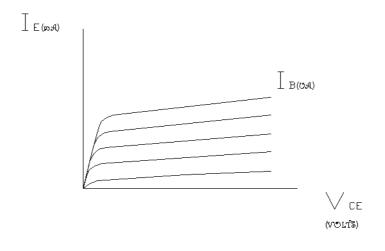

## MODEL GRAPH FOR CC CONFIGURATION:

## INPUT CHARACTERISTICS

## **OUTPUT CHARACTERISTICS**

#### **Output characteristics:**

The base current  $I_B$  is kept constant at a suitable value by adjusting e emitter collector voltage  $V_{CE}$ . The magnitude of collector emitter voltage  $V_{CE}$  is increased in suitable equal steps from zero and the emitter current  $I_E$  is noted for each setting  $V_{CE}$ . Now the curves of  $I_E$  versus  $V_{CE}$  are plotted for different constant values of  $I_B$ .

## **PROCEDURE:**

## **Input characteristics:**

- 1. Keeping the voltage across collector to emitter ( $V_{CE}$ ) as constant, tabulate the values of base current for various values of base collector voltage ( $V_{BC}$ ).

- $_{\rm 2.}$  Repeat the same procedure for various values of  $V_{\rm CE.}$

## **Output characteristics:**

- 1. Keeping the base current as constant, tabulate the values of emitter current  $(I_E)$  for various values of collector emitter voltage  $(V_{CE})$ .

- 2. Repeat the same procedure for various constant values of base current  $(I_B)$ .

| $\mathbf{V}_{\mathbf{CE}(\mathbf{v})} = \mathbf{v}$ |                    | $V_{CE(V)} = v$    |                    | $V_{CE(v)} = v$    |                    |

|-----------------------------------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| V <sub>BC(v)</sub>                                  | I <sub>B(µA)</sub> | V <sub>BC(V)</sub> | I <sub>B(μA)</sub> | V <sub>BC(V)</sub> | I <sub>B(µA)</sub> |

|                                                     |                    |                    |                    |                    |                    |

## TABULATION FOR CC CONFIGURATION: INPUT CHARACTERISTICS

## **OUTPUT CHARACTERISTICS**

| $I_B = \mu A$       |                     | $I_B = \mu A$       |                    | $I_B = \mu A$       |                     |

|---------------------|---------------------|---------------------|--------------------|---------------------|---------------------|

| V <sub>CE (V)</sub> | I <sub>E (mA)</sub> | V <sub>CE (V)</sub> | I <sub>E(mA)</sub> | V <sub>CE (V)</sub> | I <sub>E (mA)</sub> |

|                     |                     |                     |                    |                     |                     |

|                     |                     |                     |                    |                     |                     |

|                     |                     |                     |                    |                     |                     |

|                     |                     |                     |                    |                     |                     |

|                     |                     |                     |                    |                     |                     |

|                     |                     |                     |                    |                     |                     |

|                     |                     |                     |                    |                     |                     |

|                     |                     |                     |                    |                     |                     |

|                     |                     |                     |                    |                     |                     |

|                     |                     |                     |                    |                     |                     |

|                     |                     |                     |                    |                     |                     |

|                     |                     |                     |                    |                     |                     |

**MODEL CALCULATION:**

**RESULT:**

## **DISCUSSION QUESTIONS:**

## 1. What do understand by dc and ac load line?

DC load line: the output characteristics of a transistor circuit which gives the values of  $I_C$  and  $V_{CE}$  corresponding to zero signal or dc conditions.

AC load line: output characteristics of a transistor circuit which gives the values of  $I_C$  and  $V_{CE}$  when signal is applied.

## 2. List the advantages and disadvantages of fixed bias method?

- Stability of operating point is improved.

- Less cost and simple circuit.

## 3. List the disadvantages of fixed bias method?

- Stability is poor

- When temperature changes, leads to thermal runaway problem.

## 4. What do you meant by Emitter Follower?

CC amplifier is called as output, and it exactly follows the input voltage variation.

#### 5. What is the condition for avoiding thermal runaway problem?

The rate of release of heat at collector junction JC should be less than the rate of heat dissipation under  $\partial P_m / \partial T_c < \partial P_d / \partial Tc$ .

#### 6. Comparison of transistor configuration?

| Characteristics  | СВ                        | СЕ               | CC                    |

|------------------|---------------------------|------------------|-----------------------|

| Input            | Low(about $100\Omega$ )   | Low(about 750KΩ) | High(about            |

| impedance        |                           |                  | 750kΩ)                |

| Output impedance | Very high(about<br>450kΩ) | High(about 45kΩ) | Low(about 50Ω)        |

| Voltage gain     | About 150                 | About 500        | Less than 1           |

| Application      | High frequency            | Audio frequency  | Impedance<br>matching |

## 7. List the uses of emitter follower circuit?

• Used in electronic instruments because of low output impedance and high input impedance.

• Used for impedance matching.

## 8. List the advantage of CC configuration?

- High input impedance

- Low output impedance

- Voltage gain is nearly 1.

#### 9. Define h parameters?

Hybrid parameter means mixed parameters. Actually these parameters have mixed dimensions and hence they are called as h parameters. The parameters ( $h_{fe}$  and  $h_{re}$ ) are dimensionless.

## 10. What are the limitations of h parameters?

- h parameters an subjected to variation due to temperature Q point is varied as resulting this it in lightly difficult to compute accurately.

- Transistor behaves as a two point network for small signal only, hence h parameters can be used to analyze only the small signal amplifiers.

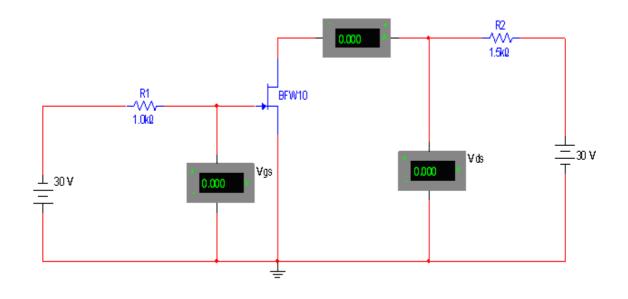

# **CIRCUIT DIAGRAM FOR JFET:**

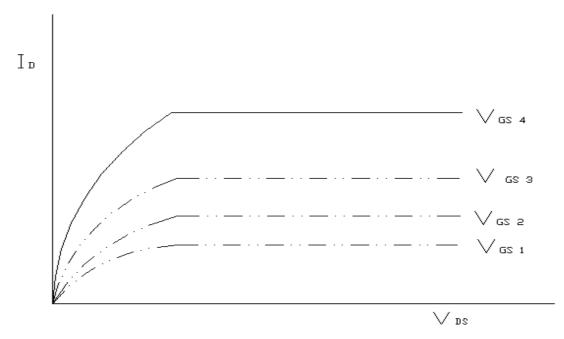

MODEL GRAPH FOR JFET:

# DRAIN CHARACTERISTICS

#### CHARACTERISTICS OF JFET

## Ex.No: Date:

#### AIM:

To draw the drain and transfer characteristics and determine the transconductance, drain resistance and amplification factor of the given JFET.

#### **APPARATUS REQUIRED:**

| Sl.No. | Apparatus        | Range    | Quantity    |

|--------|------------------|----------|-------------|

| 1.     | RPS              | (0-30)V  | 2           |

| 2.     | Resistor         | 1ΚΩ      | 1           |

|        |                  | 1.5 ΚΩ   | 1           |

| 3.     | Voltmeter        | (0-10)V  | 1           |

|        |                  | (0-30)V  | 1           |

| 4.     | JFET             | BFW10    | 1           |

| 5.     | Ammeter          | (0-10)mA | 1           |

| 6.     | Bread board      | -        | As required |

| 7.     | Connecting wires |          | As required |

|        |                  |          |             |

#### FORMULA USED:

Drain Resistance  $R_d = \Delta V_{DS} / \Delta I_{D}$ ,  $V_{GS}$  as constant

Amplification factor  $\mu = g_m r_d$

Transconductance  $~g_m$  =  $\Delta I_D \!/ \Delta V_{GS}$  ,  $V_{DS}$  as constant

#### **THEORY:**

FET is a three terminal device which current is controlled an electrified. The operation of FET depends only on the majority carriers.

#### **OPERATION:**

When  $V_{GG}$  applied  $V_{DD} = 0$

The P-type gate and N-type channel constitute PN junction is always reverse biased in JFET operation. The reverse bias is applied by a battery voltage,  $V_{GG}$  connected between the gate and the source terminal. When PN junction is reverse biased, the electrons and holes diffuse across the junction and leave behind the

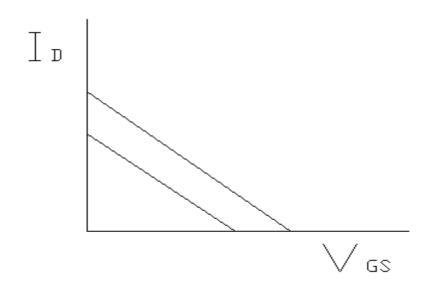

## TRANSFER CHARACTERISTICS

## **TABULATION FOR JFET:**

#### **DRAIN CHARACTERISTICS**

| V <sub>GS</sub>     | = V                 | V <sub>GS</sub>     | = V                 | $V_{GS} =$          | V                   |

|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| V <sub>DS</sub> (v) | I <sub>D</sub> (mA) | V <sub>DS</sub> (v) | I <sub>D</sub> (mA) | V <sub>DS</sub> (v) | I <sub>D</sub> (mA) |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

positive ions on N side and negative ions on P side. The region containing immobile ions is known as **Depletion region.** Both regions are heavily doped, then the depletion region symmetrically on both sides.

When no  $V_{DD}$  is applied the depletion region is a symmetrical and the conductivity's zero, since there are no mobile carriers in the junction. As the reverse bias voltage across the junction is increased, thickness of the depletion region also increases.

#### When $V_{DD}$ applied $V_{GG} = 0$

When no voltage is applied to gate i.e  $V_{GG}=0$  and  $V_{DD}$  is applied between source and drain. The electron will flow from source to drain through the channel.

#### When $V_{DD}$ applied $V_{GG}$ is applied

When voltage is applied between the drain and source with a battery  $V_{DD}$ , the electrons flow from source to drain through the narrow channel existing between the depletion regions.

#### **TRANSFER CHARACTERISTICS:**

The curves shows the relationship between drain current ( $I_D$ ) and gate to source voltage ( $V_{GS}$ ) for different values of drain source ( $V_{DS}$ ) voltage. First adjust the drain to source voltage to some suitable value. Then increase the gate to source voltage in small suitable value at each step and record the corresponding values of drain current at each step. If  $V_{GS}$  continuously increasing, the channel width reduced when  $V_{GS} = V_P$ , the pinch off occurs thus  $I_D = 0$ . **DRAIN CHARACTERISTICS:**

It shows the relation between the drain to source voltage (V\_DS) and drain current ( $_{\mbox{\scriptsize ID})}.$

#### **Active Region**:

In this region the for a small increase in drain to source voltage the drain current increases largely. Hence this is called active region.

#### **Cut off region:**

In this region the current never increases even if voltage increases. Hence it is called cutoff region.

#### Saturation region:

In this region after increasing from active region, the drain current remains constant over a range of drain to source voltage. After that current

| V <sub>DS</sub>     | = V                 | $\mathbf{V}_{\mathrm{DS}} = \mathbf{V}$ $\mathbf{V}_{\mathrm{DS}} =$ |                     | V                   |                     |

|---------------------|---------------------|----------------------------------------------------------------------|---------------------|---------------------|---------------------|

| V <sub>GS</sub> (V) | I <sub>D</sub> (mA) | V <sub>GS</sub> (V)                                                  | I <sub>D</sub> (mA) | V <sub>GS</sub> (V) | I <sub>D</sub> (mA) |

|                     |                     |                                                                      |                     |                     |                     |

|                     |                     |                                                                      |                     |                     |                     |

|                     |                     |                                                                      |                     |                     |                     |

|                     |                     |                                                                      |                     |                     |                     |

|                     |                     |                                                                      |                     |                     |                     |

|                     |                     |                                                                      |                     |                     |                     |

|                     |                     |                                                                      |                     |                     |                     |

|                     |                     |                                                                      |                     |                     |                     |

|                     |                     |                                                                      |                     |                     |                     |

|                     |                     |                                                                      |                     |                     |                     |

|                     |                     |                                                                      |                     |                     |                     |

|                     |                     |                                                                      |                     |                     |                     |

|                     |                     |                                                                      |                     |                     |                     |

## TRANSFER CHARACTERISTICS

#### **MODEL CALCULATION:**

pinches off or shoots to a very high value. The drain to source voltage at which it occurs is called as pinch off Voltage.

#### **PROCEDURE:**

- 1. The connections are given as shown in circuit diagram.

- 2. By varying RPS1  $V_{GS}$  is kept constant.

- 3. Now  $V_{DS}$  is varied and corresponding variation in drain current  $I_D$  is tabulated.

- 4. This process is repeated for another value of  $V_{GS}(V_{GS}$  is set at -1 V and -2Volts)

- 5. Plot these values on graph with  $V_{GS}$  on x axis and  $I_D$  on Y axis. This gives the drain characteristics.

- 6. By varying RPS2, it is kept at constant value. Say  $V_{DS} = 2V$ .

- 7. Now for various values of VGS, drain current is  $taken(I_D)$ . This is repeated for another value of  $V_{DS}$ .

- 8. Plot these values on graph sheet with  $V_{GS}$  on X axis and  $I_D$  on Y axis. This gives us Transfer characteristics.

- 9. The various parameters are found as given in formula used.

**RESULT:**

#### **DISCUSSION QUESTIONS:**

#### 1. What is a FET?

A field effect (FET) is a three terminal semiconductor device in which current conduction takes place by one type of carriers (either holes or electron) and is controlled by an electric field.

#### 2. Why FET is called an unipolar device?

The operation of FET depends upon the flow of majority carriers only (either holes or electrons) the FET is said to be unipolar device.

#### **3. Define pinch off voltage?**

It is the voltage at which the channel is pinched off, i.e. all the free charge from the channel get removed.

#### 4. Define drain resistance?

Drain resistance (r<sub>d</sub>) is defined as the ratio of small change in drain to source voltage ( $\Delta V_{ds}$ ) to the corresponding change in drain current ( $\Delta I_d$ ) at constant gate to source voltage ( $V_{gs}$ ).  $r_d = \Delta V_{ds} / \Delta I_d$  at constant gate to source voltage ( $V_{gs}$ )

#### 5. Write down the relationship between various FET parameters?

Amplification factor = drain resistance \* Transconductance

$\mu = r_d * g_m$

#### 6. Mention the application of FET?

- Used as a low noise amplifier

- Used as a buffer amplifier

- Used as phase shift oscillator

#### 7. Why the input impedance of FET is more than that of a BJT?

The input impedance of FET is more than that of a BJT because the input circuit of FET is reverse biased whereas the input circuit of BJT is forward biased.

#### 8. What is meant by gate source threshold voltage of a FET?

The voltage at which the channel is completely cur off and the drain current becomes zero is called as gate source threshold voltage.

#### 9. Why N channel FET's are preferred over P channel FET's?

In N channel FET the charge carriere are the electrons which have a mobility o9f about 1300 cm<sup>2</sup>/VS, whereas in P channel FET's the charge carriers are the holes which have a mobility of about 500 cm<sup>2</sup> /VS. the current in a semiconductor is directly proportional to mobility. Therefore the current in N channel FET is more than that of P channel FET.

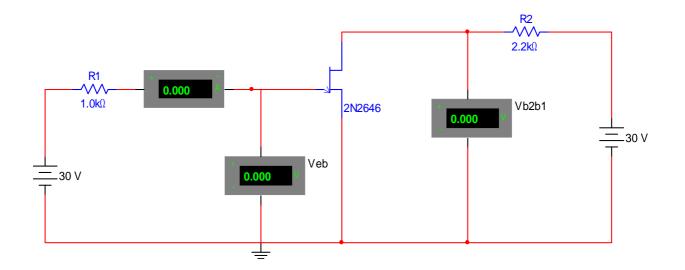

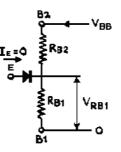

## **CIRCUIT DIAGRAM FOR UJT:**

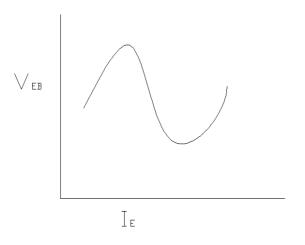

## **UJT CHARACTERISTICS:**

## Ex.No: CHARACTERISTICS OF UJT

Date:

## AIM:

To determine the static characteristics of UJT.

## **APPARATUS REQUIRED:**

| S.No. | Apparatus        | Range       | Quantity    |

|-------|------------------|-------------|-------------|

| 1.    | RPS              | (0-30)V     | 2           |

| 2.    | Voltmeter        | (0-10)V     | 2           |

| 3.    | Ammeter          | (0-100)mA   | 1           |

| 4.    | Resistance       | 1K <b>Ω</b> | 1           |

|       |                  | 1.5ΚΩ       | 1           |

| 5.    | UJT              | 2N2646      | 1           |

| 6.    | Connecting wires |             | As required |

| 7.    | Read Board       |             | As required |

#### FORMULA USED:

- 1. Negative Resistance =  $\Delta V_{BE} / \Delta I_E$  /  $V_{B1B2}$

- 2. Intrinsic Stand off ratio =  $V_P V_{BE/}V_{B1B2}$

#### **THEORY:**

The Uni Junction Transistor is a three terminal device. It has three terminals. Emitter, Base1 and base2. It consists of N type semiconductor bar into which P-Type semi conductor material is diffused. Contacts are then made into the device. The fig.1 shows the equivalent circuit of a n UJT.

## **TABULATION FOR UJT:**

| $I_{E(\mu A)}$ | V <sub>EB(V)</sub> | $I_{E(\mu A)}$ |

|----------------|--------------------|----------------|

|                |                    |                |

|                |                    |                |

|                |                    |                |

|                |                    |                |

|                |                    |                |

|                |                    |                |

|                |                    |                |

|                |                    |                |

|                |                    |                |

|                |                    |                |

|                |                    |                |

|                |                    |                |

|                |                    |                |

## **MODEL CALCULATION:**

Fig.1.Equivalent circuit of UJT

#### **OPERATION:**

From the characteristics of UJT up to the peak point, the diode is reverse biased, and hence to the left of the peak point is known as cut off voltage. The voltage corresponding to this point is peak voltage. In the cut off region PN junction is reverse biased. The device does not conduct, only a small amount of current flows through the device. Once peak point is reached the device starts conducting. UJT has negative resistance characteristics. The device conducts up to one point which is called valley point. After the valley point the device passes to a saturation region. In this region the device voltage and current reach standard values.

#### **PROCEDURE:**

- 1. Connections are made as per the circuit diagram.

- 2. The voltage  $V_{B1B2}$  is kept as constant.

- 3. Varying the RPS1 the voltmeter readings of  $V_{EB1}$  and ammeter  $I_E$  readings are note down.

- 4. The above process is repeated for different values of  $V_{B1B2}$  readings.

- 5. At one point the needle deflects back and current starts increasing.

- 6. The current must not increase beyond 25mA.

- 7. The graph between  $V_{EB1}$  and  $I_E$  are plotted.

**RESULT:**

#### **DISCUSSION QUESTIONS:**

#### 1. What does UJT stand for? Justify the name UJT.

UJT stands for uni junction transistor. The UJT is a three terminal semiconductor device having two doped regions. It has one emitter terminal and two base terminals. It has only one junction, moreover from the outlook; it resembles to a transistor hence the name uni junction transistor.

#### 2. What is "interbase resistance" of UJT?

The resistance between the two bases of UJT is called interbase resistance. Its typical value ranges from  $5k\Omega$  to  $10k\Omega$  with emitter open.

Interbase resistance,  $R_{bb} = R_{b1} + R_{b2}$

Where

$R_{b1}$  = resistance of silicon bar between  $B_1$  and emitter function

$R_{b2}$  = resistance of silicon bar between  $B_2$  and emitter function

#### 3. What is meant by negative resistance region of UJT?

In a UJT the emitter voltage reaches the peak point voltage (Vp), emitter current starts flowing. After the peak point any effort to increase in emitter voltage (Ve) further leads to sudden increase in the emitter current with corresponding decrease in Ve, exhibition negative resistance. This takes place until the valley point is reached. The region between the peak point and valley point is called "negative resistance region".

#### 4. How does UJT differ from a FET?

The gate junction of FET is reversed biased whereas in UJT the emitter junction is forward biased. BJT can amplify signals, whereas UJT has no ability to amplify signals.

#### 5. What are the difference between UJT and BJT?

| UJT                                                               | BJT                                                                |  |

|-------------------------------------------------------------------|--------------------------------------------------------------------|--|

| It has only one PN junction                                       | It has two PN junction                                             |  |

| Three terminals are labeled as<br>emitter(E), base(B1)& base2(B2) | Three terminals are labeled as<br>emitter(E),base(B)& collector(C) |  |

| It has no ability to amplify signals                              | It can amplify signals                                             |  |

#### 6. Mention the application of UJT?

- Used in timing circuits.

- Used in switching circuits.

- Used in phase control circuits

- Used in trigger device for SCR and TRIAC

- Used for pulse generation

#### 7. What sis source follower?

CD configuration of JFET is called as source follower because the output is taken from the source terminal of JFET. Since the output voltage closely follows the input voltage hence it is named as source follower.

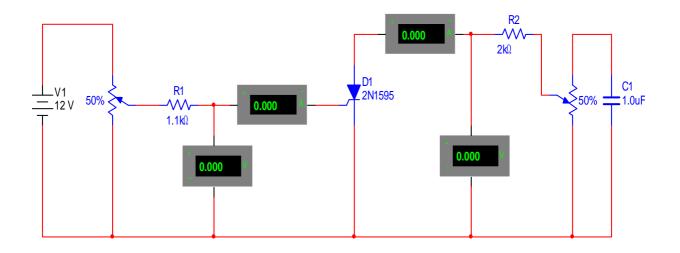

## **CIRCUIT DIAGRAM FOR SCR:**

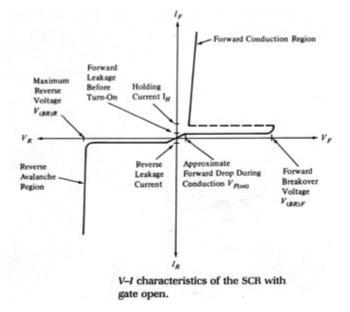

#### **MODEL GRAPH FOR SCR:**

Ex.No: Date:

#### CHARACTERISTICS OF SCR

#### AIM:

To obtain the forward and reverse characteristics of SCR and measure the holding and latching current.

#### **APPARATUS REQUIRED:**

| Apparatus | Range     | Туре   | Quantity |

|-----------|-----------|--------|----------|

| SCR       |           | TYN612 | 1        |

| RPS       | (0-30V)   |        | 2        |

| Voltmeter | (0-30V)   | МС     | 1        |

| Ammeter   | (0-500mA) | МС     | 1        |

|           | (0-50mA)  | MC     | 1        |

| Resistor  | 1300Ω/1A  |        | 1        |

|           | 470Ω      |        | 1        |

#### **THEORY:**

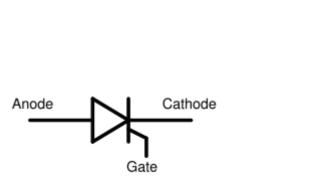

An SCR is a three terminal device. The three terminals are anode, cathode, and gate. When the anode is more positive with respect to the cathode, junctions j1,j3 are forward biased and the junctions j2 is reverse biased. Only a small leakage current

<del>و</del>

οA

Р

Ν

Р

j1

j2

j3

**Fig.2. Block Construction**

## **TABULATION FOR SCR:**

| $I_G =$             | mA                  | $I_G =$             | mA                  | $I_G =$             | mA                  |

|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| V <sub>AK</sub> (V) | I <sub>A</sub> (mA) | V <sub>AK</sub> (V) | I <sub>A</sub> (mA) | V <sub>AK</sub> (V) | I <sub>A</sub> (mA) |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

|                     |                     |                     |                     |                     |                     |

#### **MODEL CALCULATION:**

flows through the device. The device is said to be in the **forward blocking state or off state**. when the anode to cathode voltage is increased to break over value, the junction j2 breaks down and device starts conducting (ON state) the anode current must be more than the value known as latching current in order to maintain the device in the ON state. Once SCR starts conducting, it behaves like a conducting diode and gate has no control over the device. The device can be turned off only by bringing the device in below a value known as holding current. The forward voltage drop across the device in the ON state is around one volt. When the cathode voltage is made positive with respect to the anode voltage junction j2 is forward biased and the junction j1 and j3 are reversed biased. The device will be in the reverse blocking state and only small leakage current flows through the device. The device can be turned on at forward voltage less than break over voltage by applying suitable gate current.

#### **PROCEDURE:**

- 1. The connections are made as per the circuit diagram

- 2. RPS is adjusted to the required gate current flows through the device.

- 3. The  $V_{AK}$  is increased in steps by varying the RPS and each step, the corresponding anode current noted down.

- 4. Reading corresponding to Break over point, latching current, holding current and also noted down.

- 5. To determine latching current:

- 6. The forward voltage is increased to break over value, gradually. The device gets tureen ON. At this condition, the gate current is removed. If the anode current is less than the latching current, the SCR will go into OFF state immediately. The circuit resistance is repeated until the device remains in ON stat even after removing the gate current. This current is latching current.

- 7. To determine Holding current:

- 8. The gate current is removed after bringing the device into the ON state. The circuit resistance is increased in steps. The minimum value of anode current at which the SCR remains in the ON state is the holding current.

**RESULT:**

## **DISCUSSION QUESTIONS:**

#### 1. Define break over voltage of SCR?

Break over voltage is defined as the minimum forward voltage at which the SCR starts conducting heavily.

#### 2. List the advantages of SCR?

- SCR can handle and control large currents.

- Switching speed is very high.

- It has no moving parts, therefore it gives noiseless operation.

- Operating efficiency is high.

## 3. List the applications of SCR?

- Used as speed controlled in DC and AC motors.

- Used as a inverter

- Used as an converter

- Used in battery chargers

- Used for phase control and heater control

- Used in light dimming control circuits

## 4. What is meant by latching?

The ability of SCR to remain conducting even when the gate signal is removed is called latching.

#### 5. Define forward current rating of a SCR?

Forward current rating oaf a SCR is the maximum anode current that it can handle without destruction.

#### 6. List the important ratings of SCR?

- Forward break over voltage

- Holding current

- Gate trigger current

- Average forward current

- Reverse breakdown voltage

## 7. Define latch current and holding current?

**Latch current:** the maximum anode current that an SCR is capable passing without destruction.

**Holding current:** the minimum value of anode current required to keep the SCR is a position.

#### 8. Define reverse break down voltage (V<sub>BR</sub>)?

The reverse voltage (anode – negative and cathode- positive) above which the reverse breakdown occurs, breaking  $J_1$  and  $J_3$  junctions. When the SCR is reverse biased, the thickness of the  $J_2$  depletion layer during the forward bias condition is greater than the total thickness of the two depletion layers at  $J_1$  and  $J_3$ . Therefore the forward breakdown voltage  $V_{BO}$  is greater than the reverse break over voltage  $V_{BR}$ .

#### 9. Define forward break over voltage?

Forward break over voltage is the voltage above which the SCR enters the conduction region (ON state). The forward breakdown voltage is dependent on the gate bias.

#### 10. What are the losses o occurs in a thyristor during working conditions?

- 1. Forward conduction loss.

- 2. Loss due of leakage current during forward and reverse blocking

- 3. Switching losses at turn-on and turn-off

- 4. Gate triggering loss.

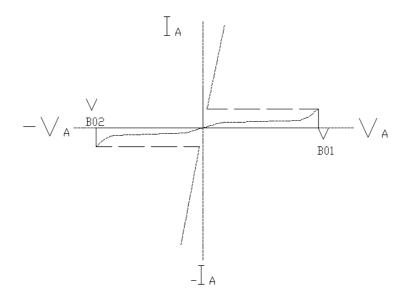

# CIRCUIT DIAGRAM FOR DIAC:

## CHARACTERISTICS OF DIAC:

#### Ex.No:

#### CHARATERISTICS OF DIAC

#### Date: AIM:

To obtain the forward and reverse characteristics of DIAC.

## **APPERATUS REQUIRED:**

| Apparatus | Range     | Туре | Quantity |

|-----------|-----------|------|----------|

| DIAC      |           |      | 1        |

| RPS       | (0-30V)   |      | 2        |

| Voltmeter | (0-30V)   | МС   | 1        |

| Ammeter   | (0-100mA) | МС   | 1        |

|           | (0-50mA)  | MC   | 1        |

| Resistor  | 1kΩ       |      | 2        |

## **THEORY:**

Diac circuits use the fact that a diac only conducts current only after a certain breakdown voltage has been exceeded. The actual breakdown voltage will depend upon the specification for the particular component type.

When the diac breakdown voltage occurs, the resistance of the component decreases abruptly and this leads to a sharp decrease in the voltage drop across the diac, and a corresponding increase in current. The diac will remain in its conducing state until the current flow through it drops below a particular value known as the holding current. When the current falls below the holding current, the diac switches back to its high resistance, or non-conducting state. Diacs are widely used in AC applications and it is found that the device is "reset" to its non-conducting state, each time the voltage on the cycle falls so that the current falls below the holding current.

## **TABULATION FOR DIAC:**

| Voltage (V <sub>A</sub> ) V | Current (I <sub>A</sub> ) mA |

|-----------------------------|------------------------------|

|                             |                              |

|                             |                              |

|                             |                              |

|                             |                              |

|                             |                              |

|                             |                              |

|                             |                              |

|                             |                              |

## **MODEL CALCULATION:**

#### **PROCEDURE:**

- 1. Connections are made as per the circuit diagram.

- 2. Keep in position minimum so Is and  $V_{\rm A}$  across MT1 and MT2 are zero.

- 3. Switch on the supply.

- 4. Allow low voltage between MT1 and MT2 increase  $V_A$  so  $I_A$  increases. Repeat it till the device turn ON.

- 5. Slowly increases gate to MT1 voltage set particular Ig = 7 mA

- 6. Keep Ig constant and increases  $V_A$  in step by step when  $V_A$  increases.  $I_A$  increases slightly when break over is reached current increases sharply.

**RESULT:**

## **DISCUSSION QUESTIONS:**

#### 1. What is DIAC?

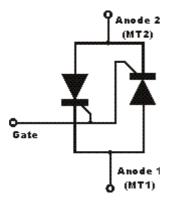

Diac is a two terminal, bidirectional semiconductor switching depending upon the polarity of the voltage applied across its main terminals. In operation diac is equivalent to two 4 layer diodes connected in antiparallel.

## 2. List the application of DIAC?

- 1. Used as a trigger device in TRIAC power control systems

- 2. Used in lamp dimmer circuits

- 3. Used in heater control circuits

- 4. Used for speed control of universal motor.

## 3. Define tunneling phenomenon?

The width of the depletion region of a reverse biased diode varies as the square root of impurity concentration. Hence with impurity concentration of 1 in 103, barrier width reduces to about 100A and there appears a non zero probability that an electron may puncture through the barrier. This is known as tunneling phenomenon.

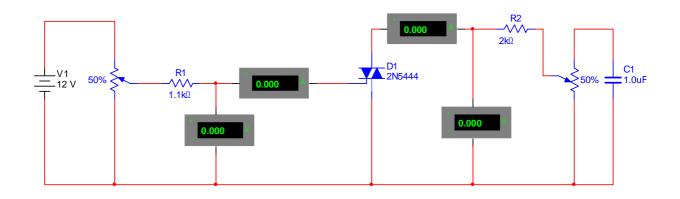

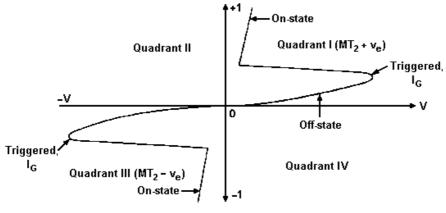

## **CIRCUIT DIAGRAM FOR TRIAC:**

# **MODEL GRAPH OF TRIAC:**

(c) v-i characteristics

## Ex.No: CHARATERISTICS OF TRIAC

Date:

## AIM:

To obtain the forward and reverse characteristics of TRIAC.

| Apparatus | Range     | Туре | Quantity |

|-----------|-----------|------|----------|

| TRIAC     |           |      | 1        |

| RPS       | (0-30V)   |      | 2        |

| Voltmeter | (0-30V)   | МС   | 1        |

| Ammeter   | (0-100mA) | МС   | 1        |

|           | (0-50mA)  | МС   | 1        |

| Resistor  | 1kΩ       |      | 2        |

## **APPERATUS REQUIRED:**

## THEORY:

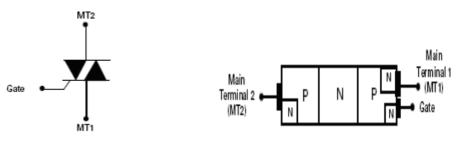

A TRIAC is a bidirectional thyristor (it can conduct in both directions) with three terminals. It is used extensively for control of power in AC circuit. When in operation, a TRIAC is equivalent to two SCRs connected in anti-parallel. Its three terminals are usually designated as MT1, MT2 and gate. The V-I characteristics of a TRIAC is based on the terminal MT1 as the reference point. The first quadrant is the region wherein MT2 is positive w.r.t MT1 and vice-versa for the third quadrant. The peak voltage applied across the device in either direction must be less the break over voltage in order to retain control by the gate. A gate current of specified amplitude of either polarity will trigger the TRIAC into conduction in either quadrant, assuming that the device is in a blocking condition initially before the gate signal is applied.

## **TABULATION FOR TRIAC:**

| $I_G = mA$         |                     | $I_G = mA$         |                     | $I_G = mA$         |                     |

|--------------------|---------------------|--------------------|---------------------|--------------------|---------------------|

| V <sub>T</sub> (V) | I <sub>A</sub> (mA) | V <sub>T</sub> (V) | I <sub>A</sub> (mA) | V <sub>T</sub> (V) | I <sub>A</sub> (mA) |

|                    |                     |                    |                     |                    |                     |

|                    |                     |                    |                     |                    |                     |

|                    |                     |                    |                     |                    |                     |

|                    |                     |                    |                     |                    |                     |

|                    |                     |                    |                     |                    |                     |

|                    |                     |                    |                     |                    |                     |

|                    |                     |                    |                     |                    |                     |

## **MODEL CALCULTION:**

Fig.1. Schematic Symbol

**Fig.2. Block Construction**

The characteristics of a TRIAC are similar to those of an SCR, both in blocking and conducting states, except for the fact that SCR conducts only in the forward direction, whereas the TRIAC conducts in both the directions

#### **PROCEDURE:**

- 1. Connections are made as per the circuit diagram.

- 2. Keep in position minimum so Is and VA across MT1 and MT2 are zero.

- 3. Switch on the supply.

- 4. Allow low voltage between MT1 and MT2 increase VA so IA increases. Repeat it till the device turn ON.

- 5. Slowly increases gate to MT1 voltage set particular Ig = 7 mA

- 6. Keep Ig constant and increases VA in step by step when VA increases. IA increases slightly when break over is reached current increases sharply.

**RESULT:**

## **DISCUSSION QUESTIONS:**

## 1. What are the applications of TRIAC?

- Phase control

- Heater control

- Motor speed control

- Light dimming control

- Static switch to turn ac power ON and OFF

## 2. What are the advantages of TRIAC?

- Triacs can be triggered with positive or negative polarity voltage

- Triac needs a single fuse for protection, which also simplifies the construction

- Triac needs a single heat sink of slightly larger size, where as antiparallel thyristor pair needs two heat sinks

- DC applications, SCR is required to be connected with a parallel diode to protect against reverse voltage, whereas a triac used work without diode, as safe breakdown in either direction is possible.

## 3. What is TRIAC?

TRIAC is a three terminal bidirectional semiconductor switching device. It can conduct in both the directions for any desired period. In operation it is equivalent to two SCR's connected in antiparallel . Next two SCR is widely used in power control.

| SCR                                                                   | TRIAC                                                                                             |  |  |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|

| It is unidirectional                                                  | It is bidirectional                                                                               |  |  |

| Triggered by narrow positive<br>pulse applied at the gate<br>terminal | Triggered by narrow pulse either<br>positive or negative polarity<br>applied at the gate terminal |  |  |

| SCR are available with a large current rating                         | Triacs are available for lower<br>current rating as compared to<br>that of SCRs                   |  |  |

# 4. Differences between SCR and TRIAC?

## 5. TRIAC is only used in AC circuits. Justify.

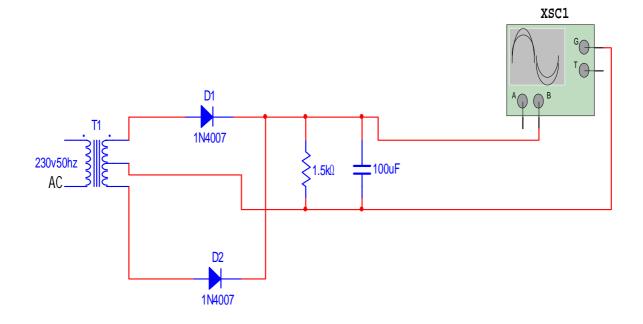

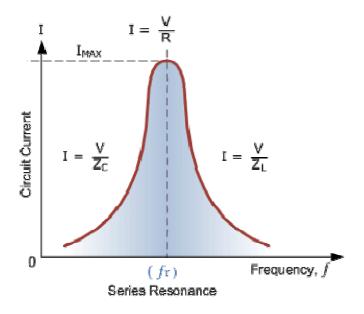

There are many applications, particularly in AC circuits, where bidirectional conduction is required. TRIAC is a bidirectional device; it can conduct in both directions. Hence TRIAC is used in AC circuits.